- support@husseinkey.com

- livechat

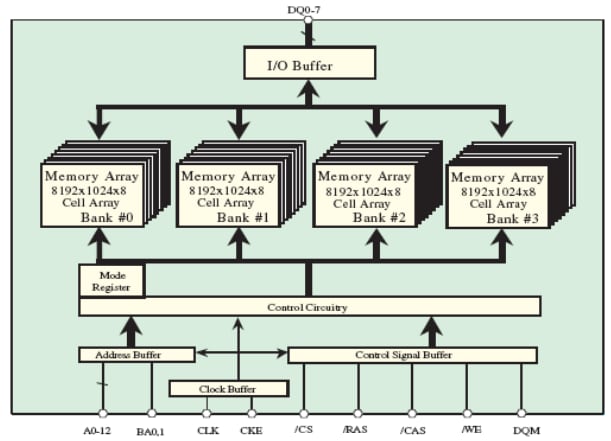

Zentel SDR SDRAM is organized as 4-bank x 8,388,608-word x 8-bit Synchronous DRAM with LVTTL interface, or 4-bank x 4,194,304-word x 16-bit. All inputs and outputs are referenced to the rising edge of CLK. The devices achieve very high-speed data rates up to 166MHz and are suitable for main memories or graphic memories in computer systems.