- support@husseinkey.com

- livechat

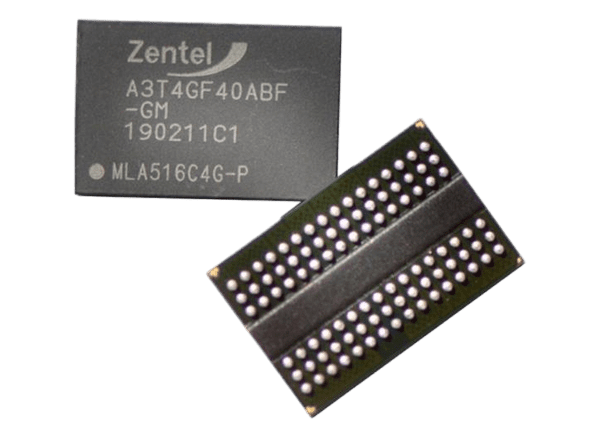

Zentel DDR3 SDRAM features a high-speed data transfer that is realized by the 8 bits prefetch pipelined architecture. The SDRAM has a double-data-rate architecture with two data transfers per clock cycle. They have a bi-directional differential data strobe (DQS and /DQS) and are transmitted/received with data for capturing data at the receiver. DQS is edge-aligned with data for READs; center-aligned with data for WRITEs. The differential clock inputs (CK and /CK) DLL aligns DQ and DQS transitions with CK transitions.