- support@husseinkey.com

- livechat

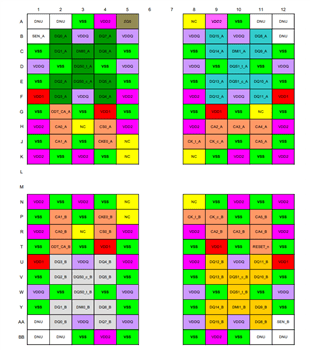

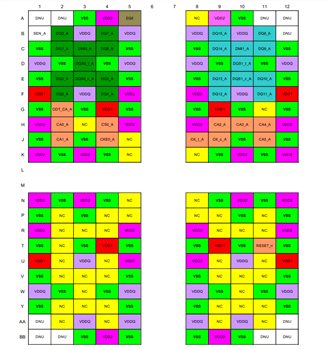

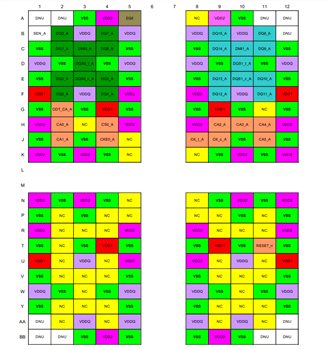

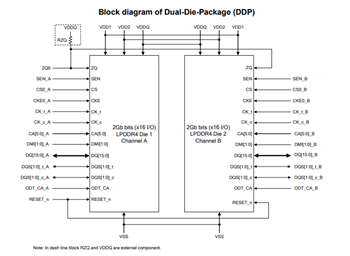

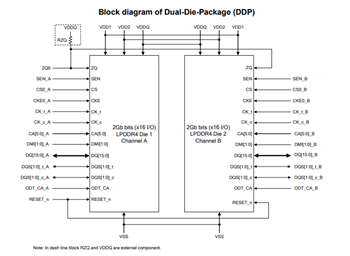

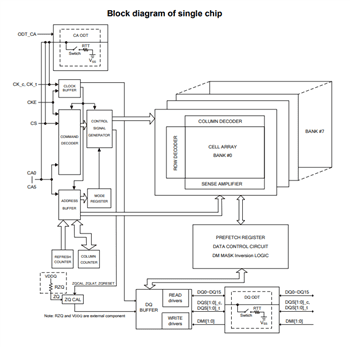

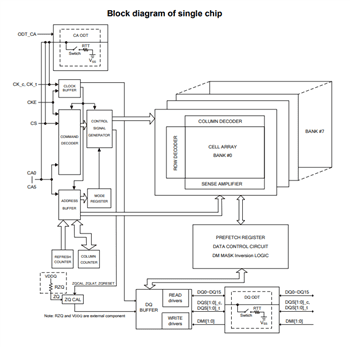

Winbond W66BP6NB/W66CP2NQ SDRAM LPDDR4 offers a Single-Die-Package (SDP) or Dual-Die-Package (DDP) and a 2 or 4 clocks architecture on the Command/Address (CA) bus. The LPDDR4 utilizes the 2 or 4 clocks architecture on the CA bus to reduce the number of input pins in the system. The 6-bit CA bus contains the command, address, and bank information. Each command uses a 1, 2, or 4 clock cycle, during which command information is transferred on the positive edge of the clock.

The Single-Die-Package (SDP) provides 16Mb x 16DQ x 8-banks x 1 channel with 2Gb (2,147,483,648 bits) density. The Dual-Die-Package (DDP) offers 16Mb x 16DQ x 8-banks x 2 channels with 4Gb (4,294,967,296 bits) density.