- support@husseinkey.com

- livechat

http://www.ti.com/general/docs/suppproductinfo.tsp?distId=26&gotoUrl=https%3A%2F%2Fwww.ti.com%2Flit%2Fgpn%2Fsn74lv4t08-q1″>View Datasheet

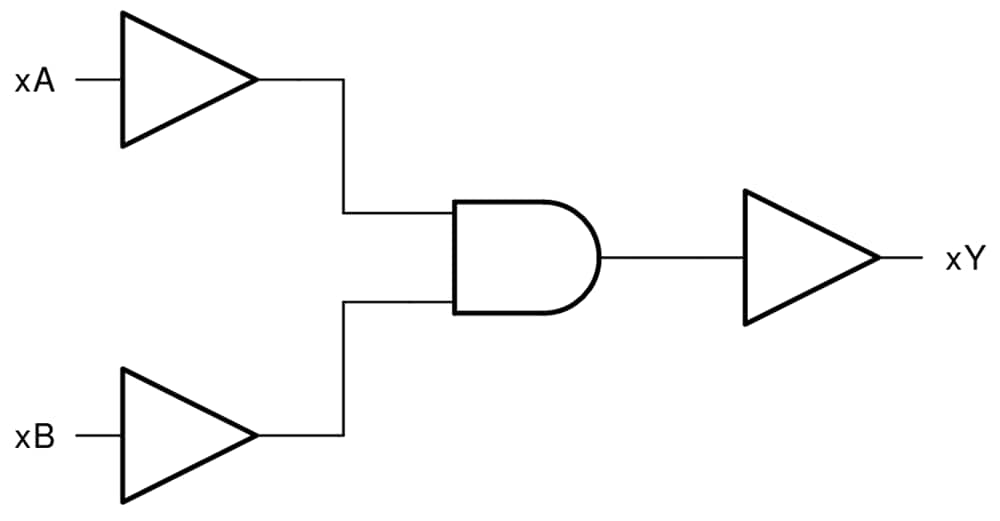

Texas Instruments SN74LV4T08/SN74LV4T08-Q1 Quad AND Gate contains four independent 2-input AND Gates with Schmitt-trigger inputs. Each gate performs the Boolean function Y = A ● B in positive logic. The output level is referenced to the supply voltage (VCC) and supports 1.8V, 2.5V, 3.3V, and 5V CMOS levels.

The Texas Instruments SN74LV4T08/SN74LV4T08-Q1 input is designed with a lower threshold circuit to support up translation for lower voltage CMOS inputs (for example, 1.2V input to 1.8V output or 1.8V input to 3.3V output). In addition, the 5V tolerant input pins enable down translation (for example, 3.3V to 2.5V output).