- support@husseinkey.com

- livechat

http://www.ti.com/general/docs/suppproductinfo.tsp?distId=26&gotoUrl=https%3A%2F%2Fwww.ti.com%2Flit%2Fgpn%2Flmk5c33414a”>View Datasheet

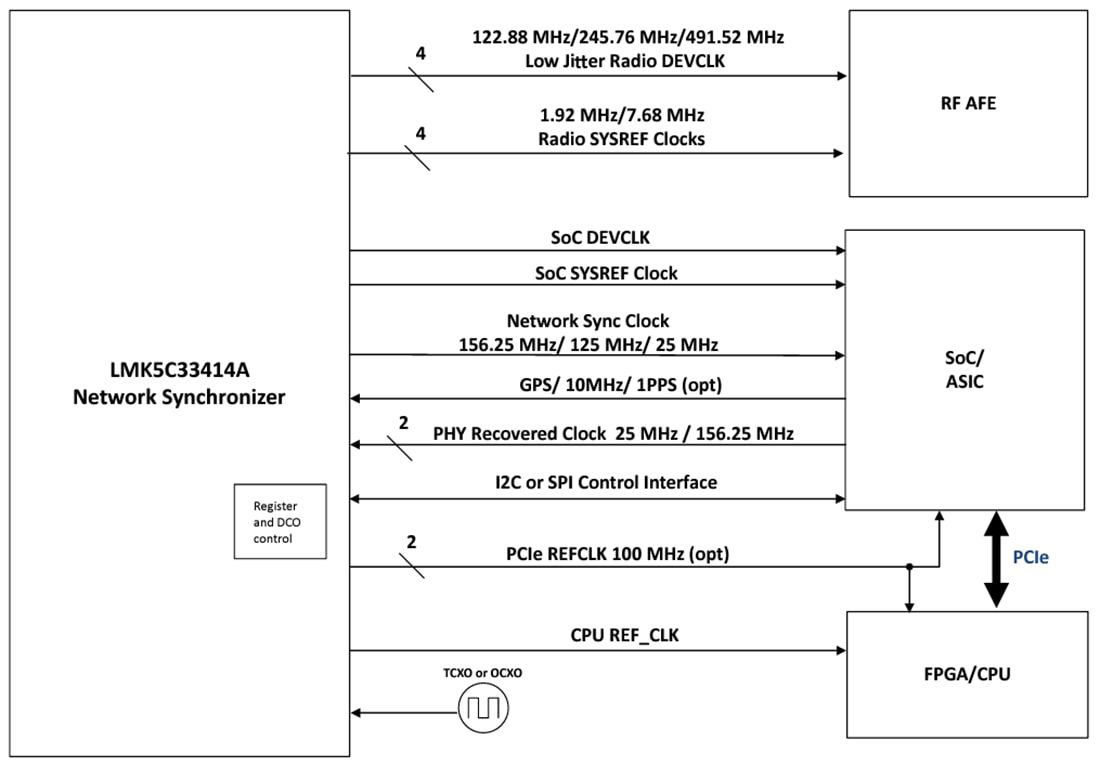

Texas Instruments LMK5C33414A High-Performance Network Synchronizer includes a jitter cleaner designed to meet stringent wireless communications and infrastructure application requirements. The network synchronizer integrates three DPLLs to provide hitless jitter and switching attenuation with programmable loop bandwidth and no external loop filters. This feature maximizes the flexibility and ease of use of the device. Each DPLL phase locks a paired APLL to a reference input.

APLL3 features ultra-high-performance PLL with TI’s proprietary Bulk Acoustic Wave (BAW) technology. It can generate 491.52MHz output clocks with 42fs typical/60fs maximum RMS jitter, irrespective of the jitter and DPLL reference input frequency characteristics. APLL2 and APLL1 provide options for a second or third frequency and/or synchronization domain.

Reference validation circuitry monitors the DPLL reference clocks and performs a hitless switch between them upon detecting a switchover event. Zero-Delay Mode (ZDM) and phase cancellation may be enabled to control the phase relationship from input to output. The Texas Instruments LMK5C33414A is fully programmable through the SPI or I2C interface. The onboard EEPROM can be used to customize the system start-up clocks. The device has factory default ROM profiles available as fallback options.