- support@husseinkey.com

- livechat

http://www.ti.com/general/docs/suppproductinfo.tsp?distId=26&gotoUrl=https%3A%2F%2Fwww.ti.com%2Flit%2Fgpn%2Fdra821u-q1″>View Datasheet

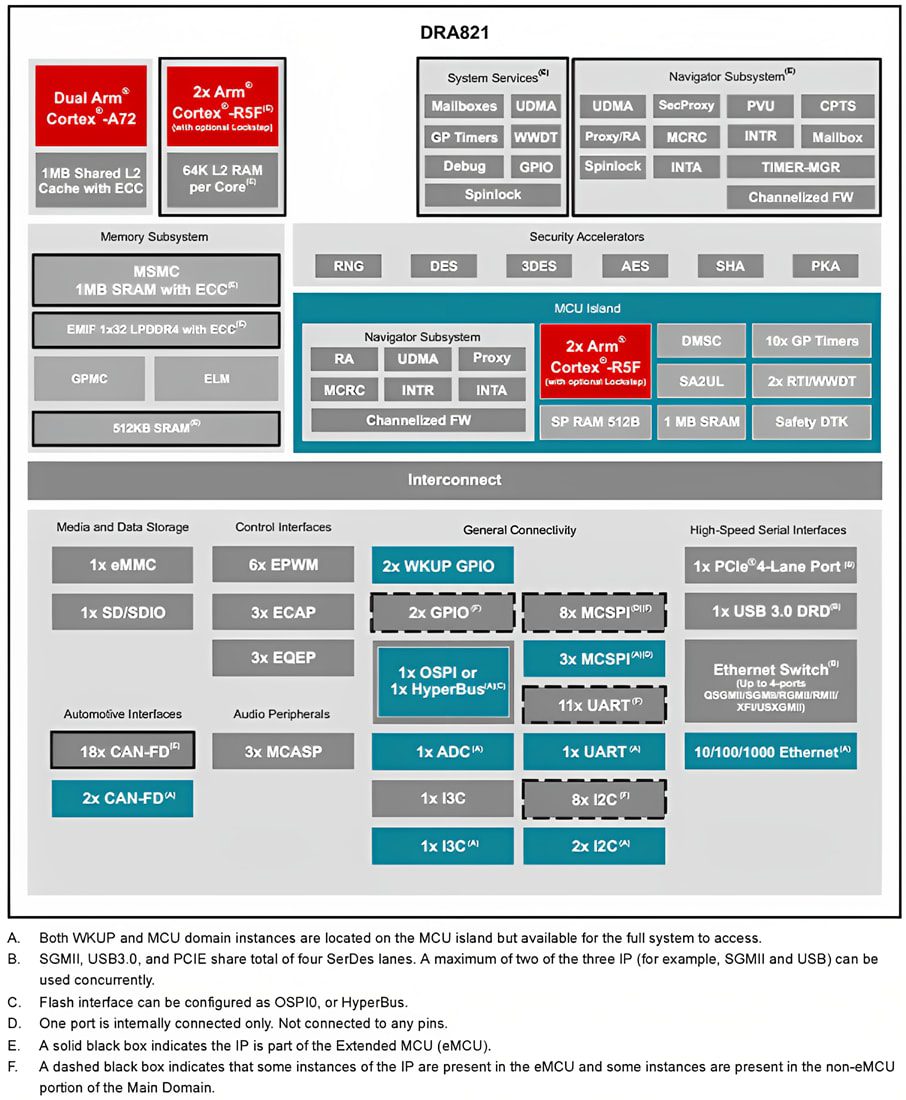

Texas Instruments DRA821x Jacinto™ 64-Bit Processors are based on the Armv8 architecture and are optimized for gateway systems with cloud connectivity. The System-on-Chip (SoC) design reduces system-level costs and complexity through integration—notably, a system MCU, functional safety and security features, and an Ethernet switch for high-speed communication. Integrated diagnostics and functional safety features are targeted to ASIL-D and SIL 3 certification requirements. A PCIe controller and a TSN-capable Gigabit Ethernet switch enable real-time control and low-latency communication.

Up to four general-purpose Arm® Cortex®-R5F subsystems can handle low-level, timing-critical processing tasks, leaving the Arm Cortex-A72 core unencumbered for advanced and cloud-based applications. The Jacinto DRA821x processors include the Extended MCU (eMCU) domain concept. This Domain is a subset of the processors and peripherals on the Main Domain targeted at higher functional safety enablement, such as ASIL-D/SIL-3. The functional block diagram highlights which IPs are included in the eMCU.