- support@husseinkey.com

- livechat

http://www.ti.com/general/docs/suppproductinfo.tsp?distId=26&gotoUrl=https%3A%2F%2Fwww.ti.com%2Flit%2Fgpn%2Fcdcbt1001″>View Datasheet

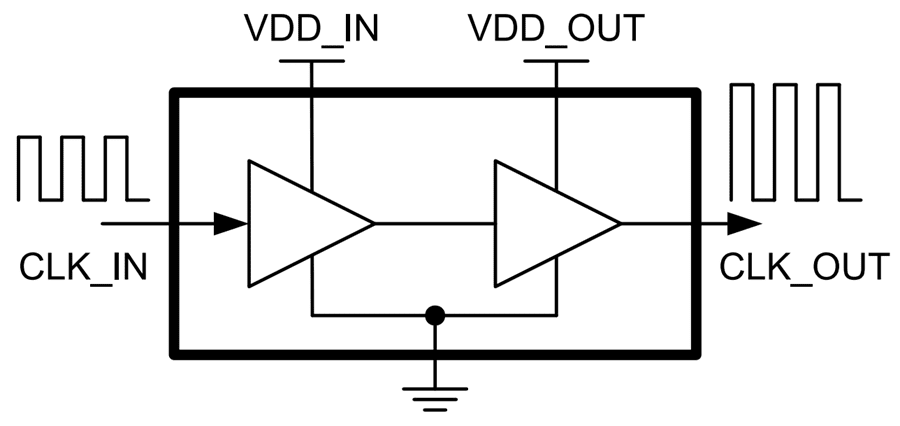

Texas Instruments CDCBT1001 Clock Buffer and Level Translator is a 1.2V to 1.8V clock buffer and level translator for personal electronics, servers, and add-in cards. The VDD_IN pin supply voltage defines the input LVCMOS clock level. The VDD_OUT pin supply voltage defines the output LVCMOS clock level. VDD_IN = 1.2V ±10%. VDD_OUT = 1.8V ±10%. The 12kHz to 5MHz additive RMS jitter at 24MHz of the Texas Instruments CDCBT1001 is less than 0.8ps.