- support@husseinkey.com

- livechat

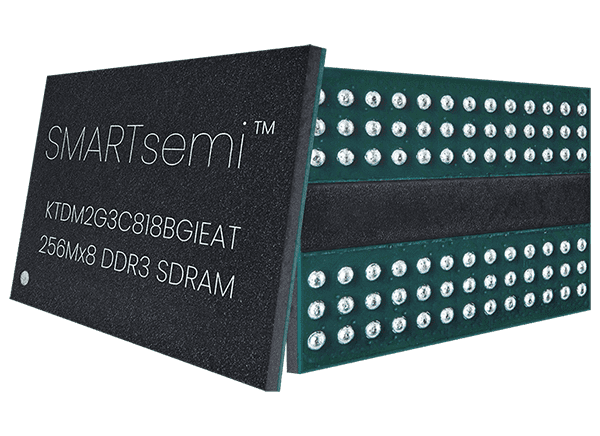

SMARTsemi DDR3 Memory ICs feature a double data rate architecture to achieve high-speed operation. The ICs achieve high-speed double-data-rate transfer rates of up to 1866Mb/sec/pin for general applications. The chip is designed to comply with all key DDR3(L) DRAM key features, and all control and address inputs are synchronized with a pair of externally supplied differential clocks.