- support@husseinkey.com

- livechat

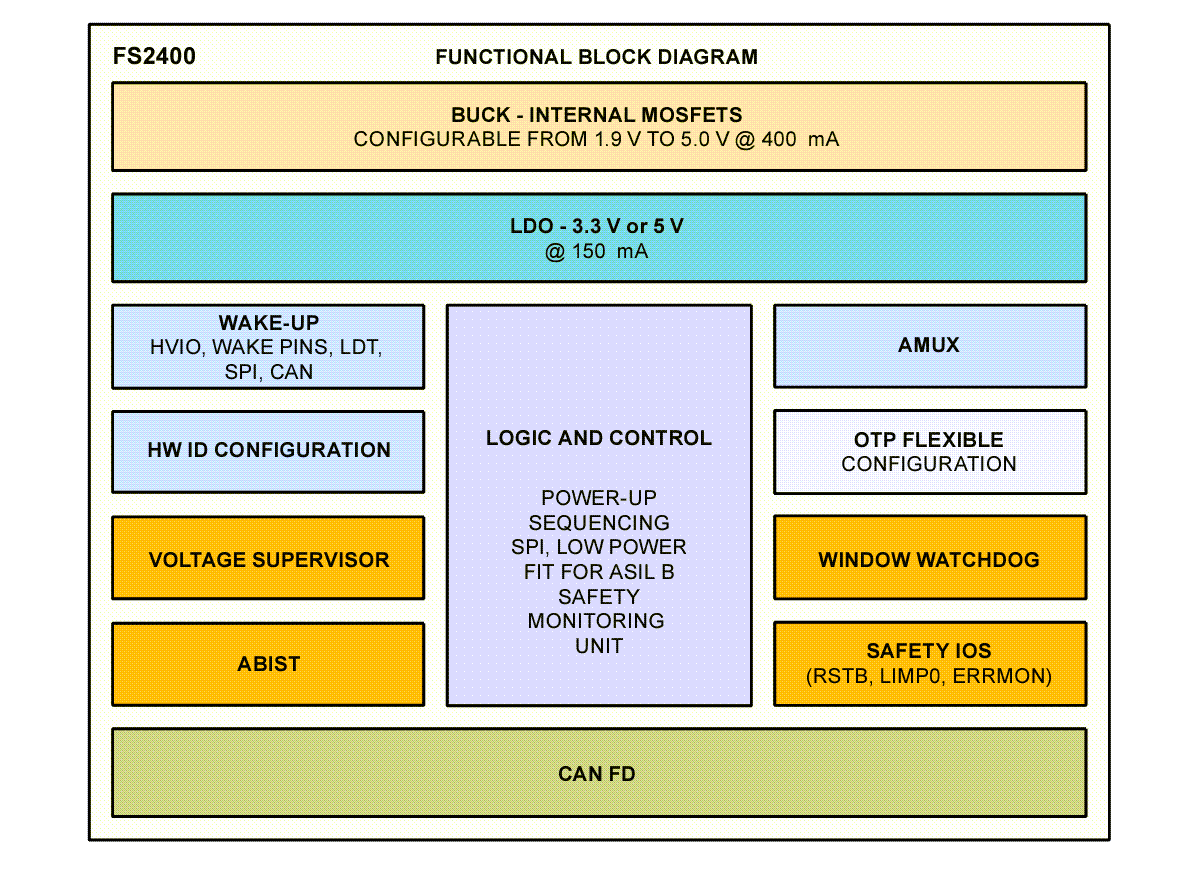

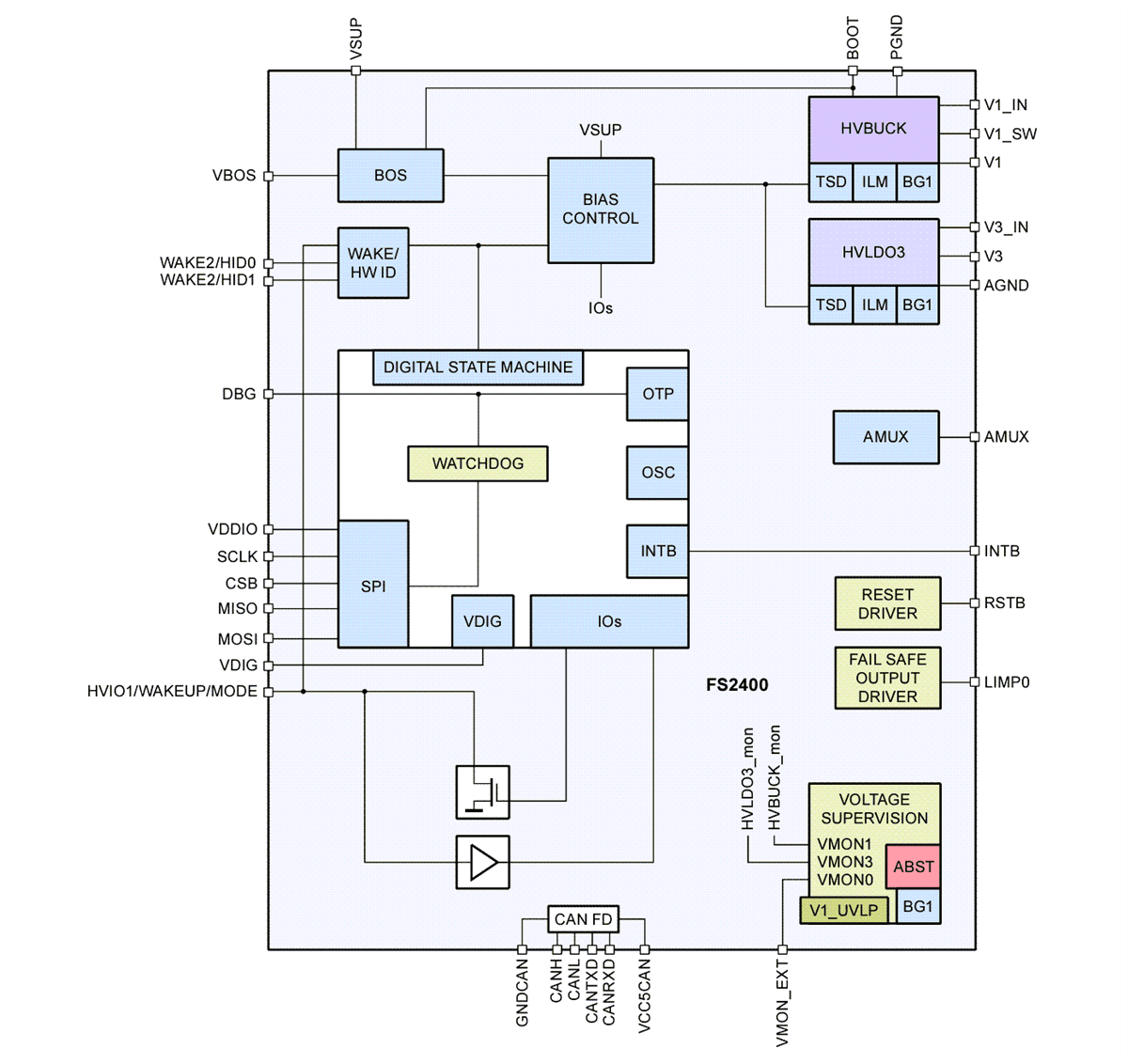

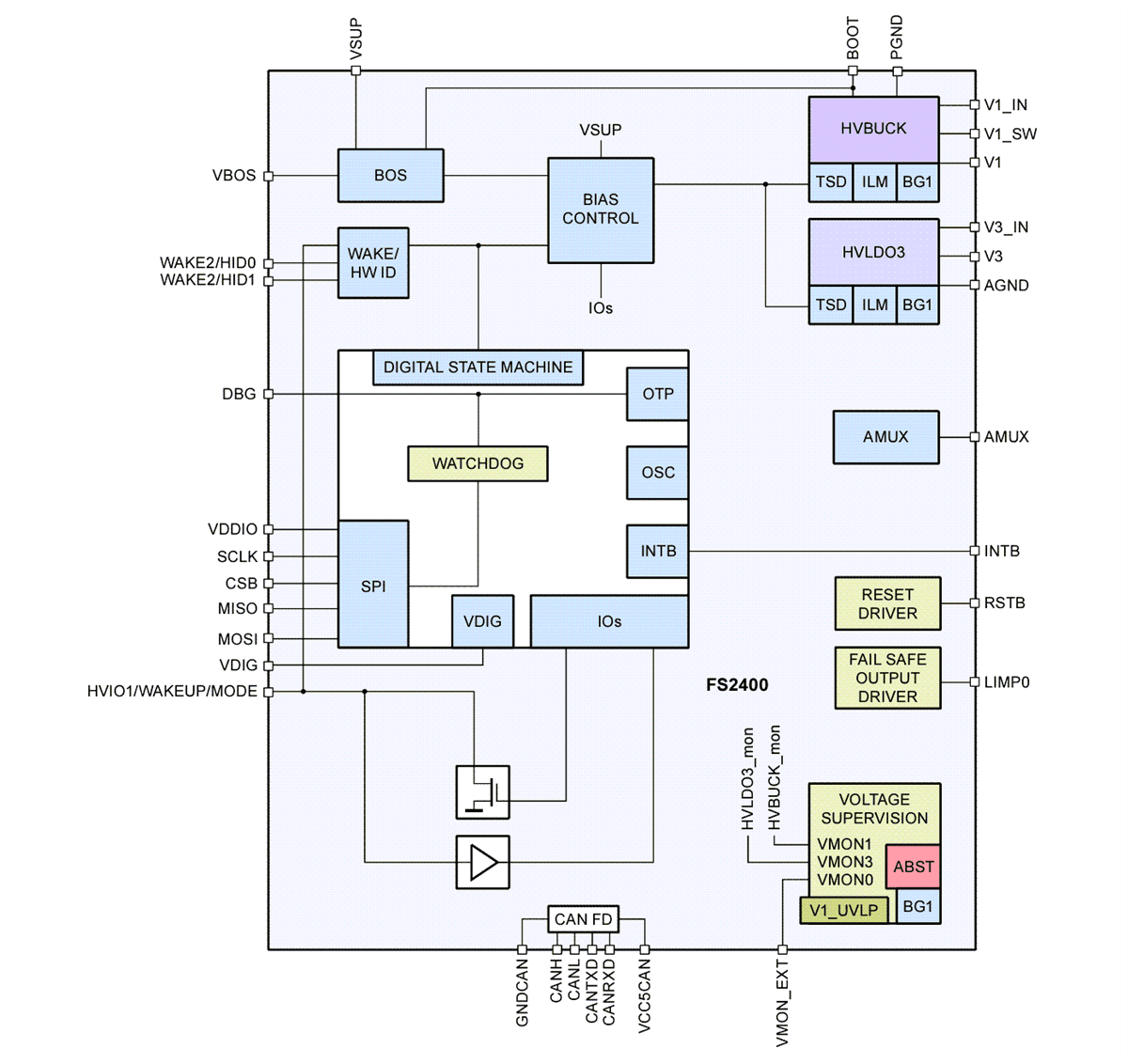

NXP Semiconductors FS2400 Fail-Safe System Basis Chips (SBCs) offer multiple power supplies developed to support secure car access utilizing ultra-wideband (UWB), near-field communication (NFC), and BLUETOOTH® Low Energy (BLE) devices. The FS2400 family of automotive safety SBCs also conform to other small applications demanding low power and CAN FD communication.

The NXP Semiconductors FS2400 Fail-Safe SBCs support a wide range of applications, delivering a choice of output voltage settings, physical interface, and integrated system-level characteristics to address low-power and noise-sensitive applications with automotive safety integrity levels (ASIL) up to ASIL B.

The FS2400 incorporates a battery-connected switched-mode regulator (V1) and a battery-connected linear regulator (V3) to equip microcontrollers, communication devices, and others. V1 provides a high-performance switching regulator capable of operating in Pulse Frequency Modulation (PFM) mode and Force Pulse Width Modulation (FPWM) mode. The mode of operation can be changed by implementing wake pins to optimize noise management.

The FS2400 is produced in compliance with the ISO 26262:2018 standard. The device includes enhanced safety features, with fail-safe output, and becomes part of a complete safety-oriented system covering ASIL B safety integrity level. The FS2400 is available in a 5mm x 5mm, 32-Ld HVQFN package with wettable flanks.