- support@husseinkey.com

- livechat

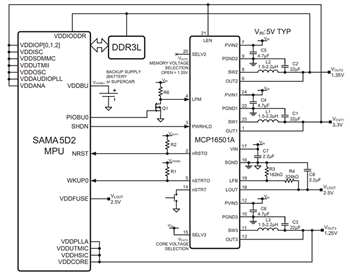

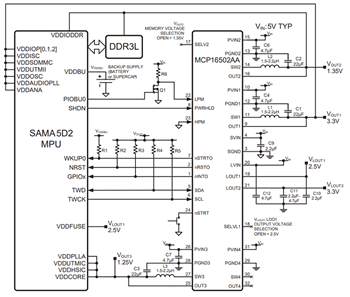

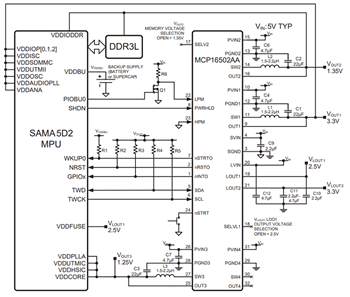

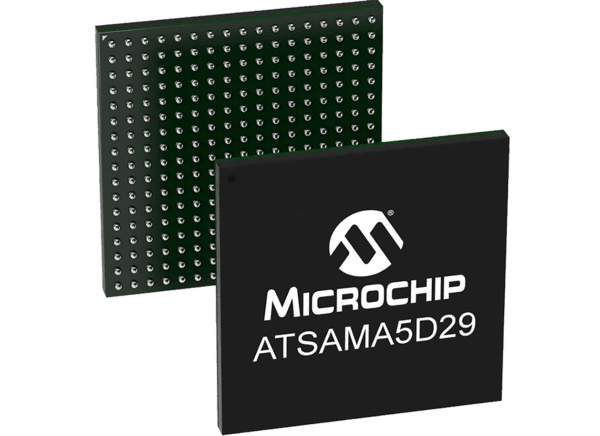

Microchip Technology SAMA5D29 Automotive Arm® Cortex®-A5 CPU-Based MPUs are high-performance, low-power embedded microprocessors running up to 500MHz. The AEC-Q100 Grade 2 qualified SAMA5D29 MPUs offer support for multiple memories such as DDR2, DDR3L, LPDDR2, LPDDR3, QSPI, and e.MMC Flash. These devices integrate powerful peripherals for connectivity and user interface applications, including two ISO-compliant CAN-FD interfaces.

Advanced security functions include Arm® TrustZone®, tamper detection, secure data storage, and secure boot. The devices also feature high-performance crypto accelerators (AES, SHA, and TRNG). The Microchip Technology SAMA5D29 Automotive MPUs are qualified for an extended, industrial -40°C to +105°C temperature range and are delivered with free Linux® distributions, MPLAB X IDE, MPLAB Harmony v3, and bare metal C examples.