- support@husseinkey.com

- livechat

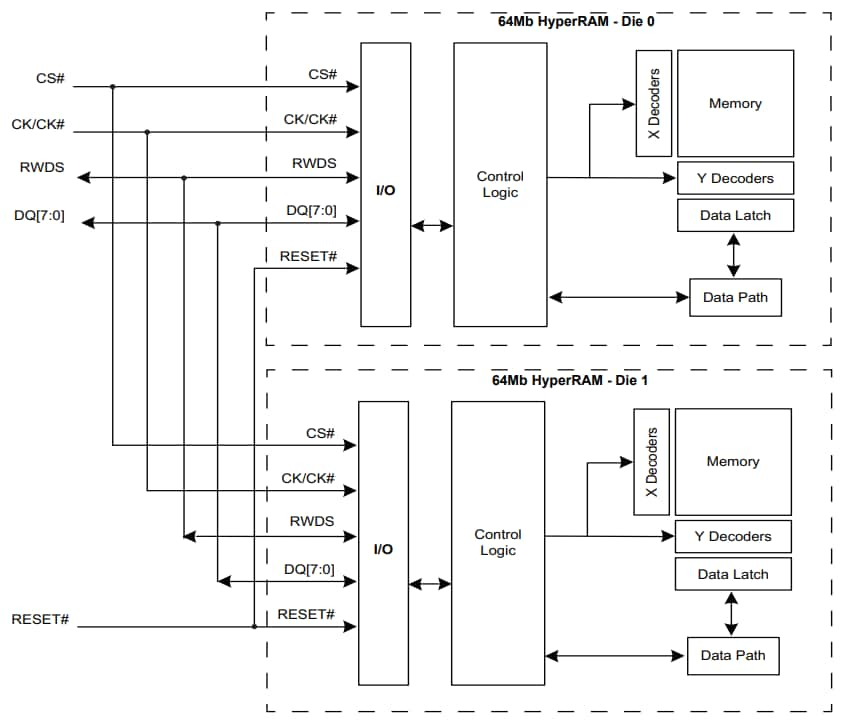

Infineon Technologies S70KL1282 and S70KL1283 Interface HyperRAMs are high-speed CMOS, self-refresh DRAMs with HYPERBUS™ interfaces. The DRAM array uses dynamic cells that require a periodic refresh. Refresh control logic within the device manages the refresh operations on the DRAM array when the memory is not being actively read or written by the HYPERBUS interface master (host). Since the host is not required to manage any refresh operations, the DRAM array appears to the host as though the memory uses static cells that retain data without refresh. The memory is more accurately described as Pseudo-Static RAM (PSRAM).