- support@husseinkey.com

- livechat

http://www.ti.com/general/docs/suppproductinfo.tsp?distId=26&gotoUrl=https%3A%2F%2Fwww.ti.com%2Flit%2Fgpn%2Fcdcdb400″>View Datasheet

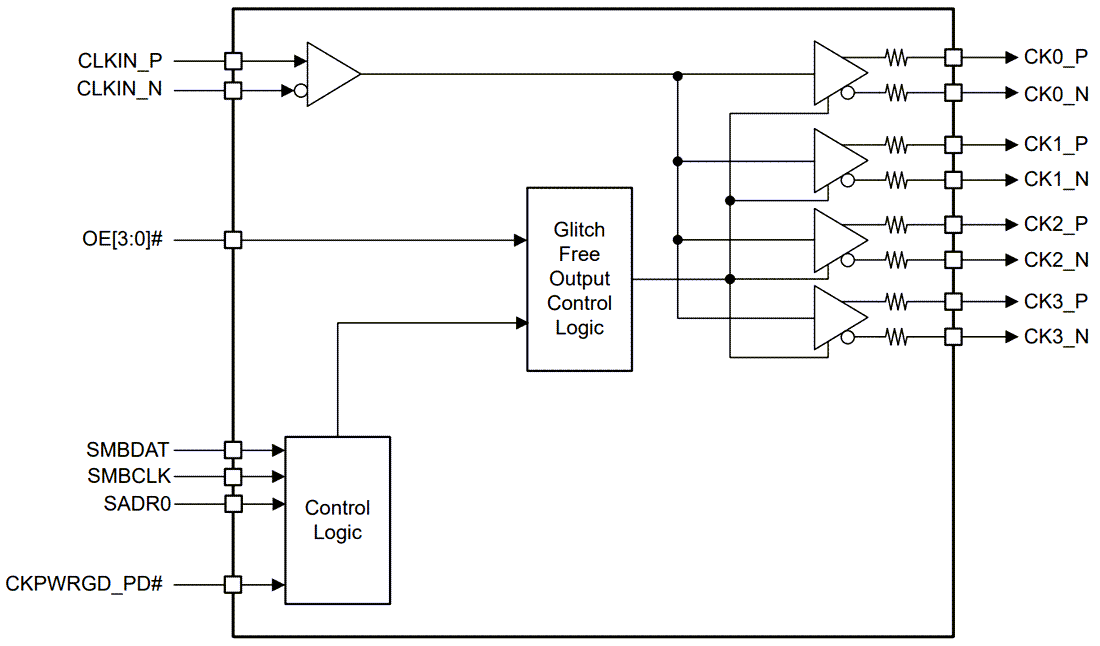

Texas Instruments CDCDB400 4-Output Clock Buffer is an LP-HCSL, DB800ZL-compliant clock buffer capable of distributing the reference clock for PCIe Gen 1-5, QuickPath Interconnect (QPI) and UPI, SAS. It can also distribute for SATA interfaces in CC, SRNS, or SRIS architectures. The SMBus interface and four output enable pins to allow the configuration and control of all four outputs individually. The CDCDB400 is a DB800ZL derivative buffer and meets or exceeds the system parameters in the DB800ZL specification. The device also meets or exceeds the parameters in the DB2000Q specification. The Texas Instruments CDCDB400 is packaged in a 5mm × 5mm, 32-pin VQFN package.