- support@husseinkey.com

- livechat

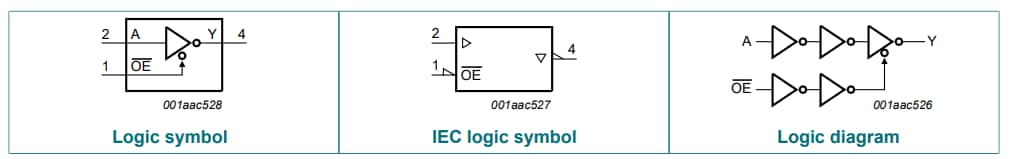

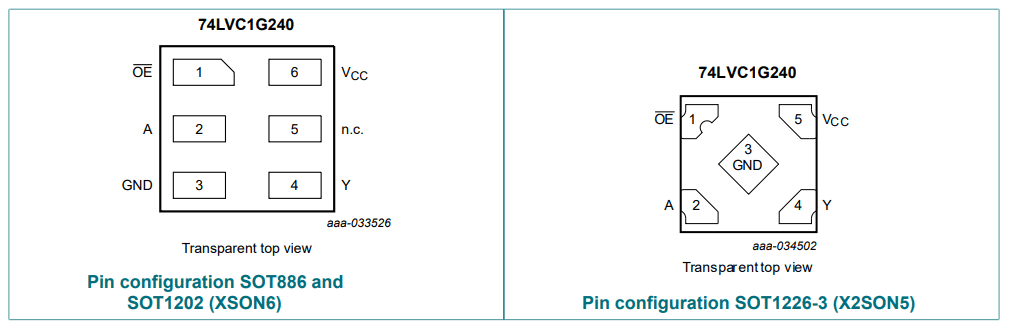

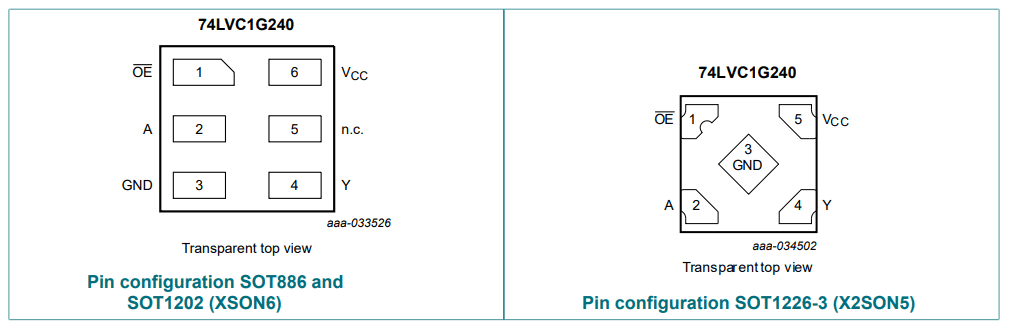

Nexperia 74LVC1G240 Single Inverting Buffer/Line Drivers are 1-bit inverting buffer/line drivers with a 3-state output. The 74LVC1G240 features an output enable OE, which outputs to enable a high-impedance OFF-state at HIGH. A 3.3V or 5V device drives the inputs for flexibility as translators in mixed 3.3V and 5V environments. The Schmitt-trigger action at all inputs makes the circuit tolerant of slower input rise and fall times.

The Nexperia 74LVC1G240 Single Inverting Buffer/Line Drivers are fully specified for partial-power-down applications using IOFF circuitry. The IOFF circuitry disables the output, preventing the potentially damaging backflow current through the 74LVC1G240 when it is powered down.