- support@husseinkey.com

- livechat

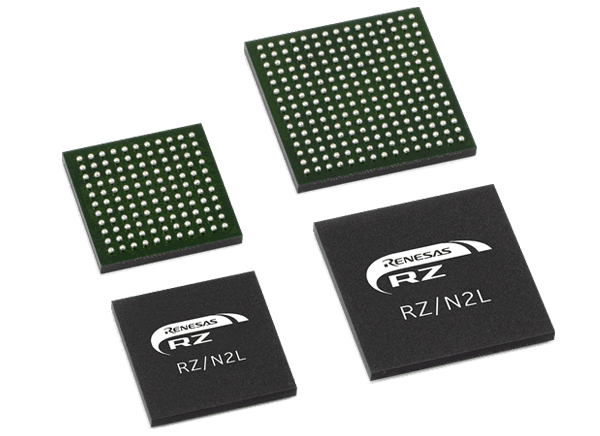

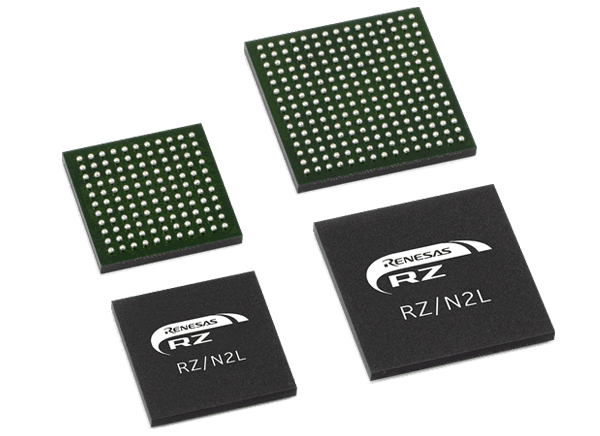

Renesas Electronics RZ/N2L Multi-Protocol Microprocessor is an LSI-optimized MPU that eases the implementation of Industrial Ethernet and TSN networks. The RZ/N2L MPU features an Arm® Cortex®-R52 core with a maximum operating frequency of 400MHz and a tightly coupled memory (256KB). The device integrates a 3-port Gigabit Ethernet switch that supports the next-generation network standard TSN and major Industrial Ethernet protocols such as EtherCAT, PROFINET, and EtherNet/IP.

The RZ/N2L MPU features a rich peripheral set utilizing a Low-Latency Peripheral Port (LLPP) bus, ideal for high-precision motor control. The device is also a full Functional Safety (FuSa) solution conforming to the ISO 26262 standards. A partitioning function can separate safety and non-safety applications to avoid interference between applications, allowing developers to reduce re-certification efforts due to the separation even if one of the non-safety applications needs to be changed or re-certified.

The Renesas Electronics RZ/N2L Multi-Protocol Microprocessor is offered in 13mm x 13mm LFBGA-225 and 10mm x 10mm LFBGA-121 packages and features a -40°C to +125°C operating junction temperature range.