- support@husseinkey.com

- livechat

http://www.ti.com/general/docs/suppproductinfo.tsp?distId=26&gotoUrl=https%3A%2F%2Fwww.ti.com%2Flit%2Fgpn%2Fam6421″>View Datasheet

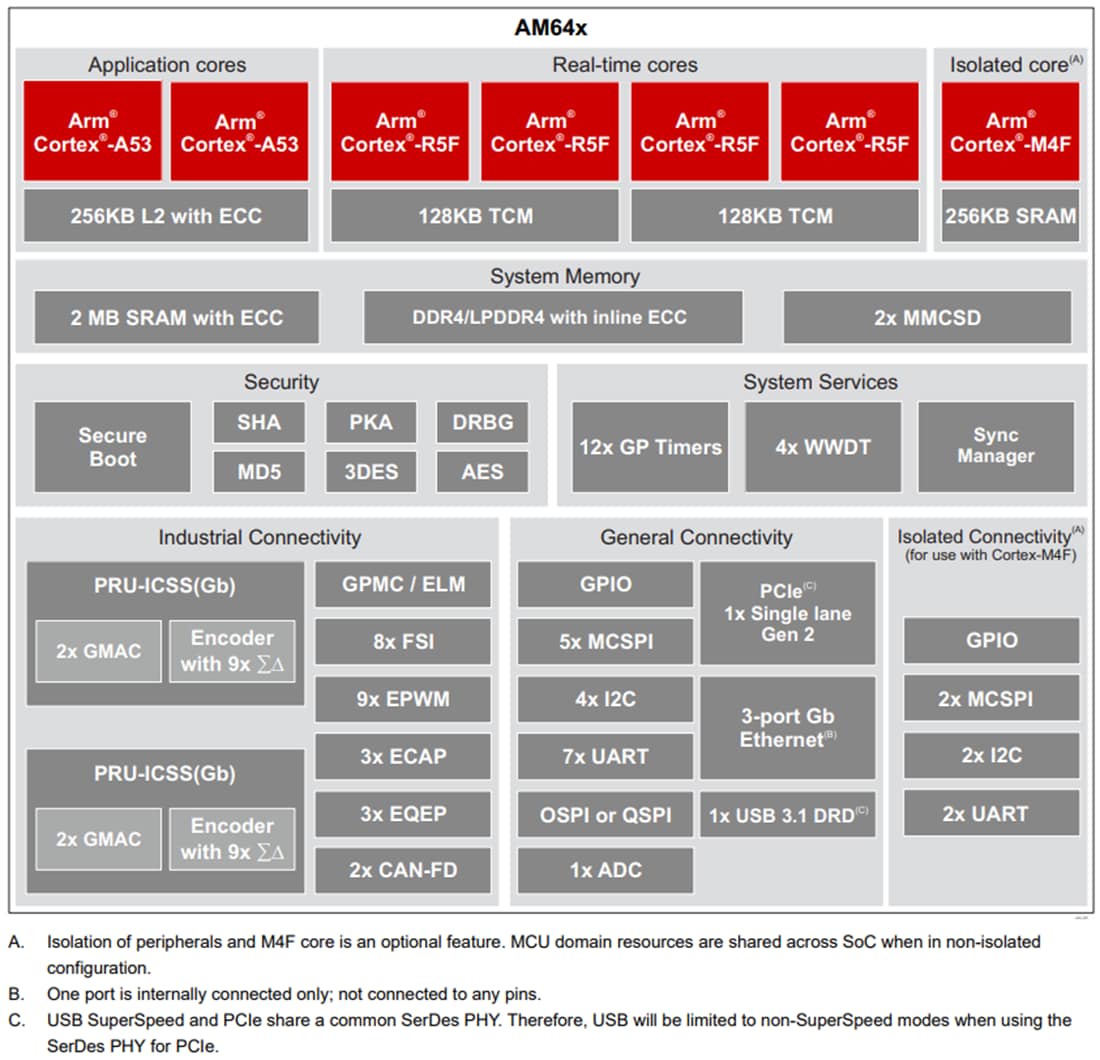

Texas Instruments AM64x Arm®-Based Single-Core Cortex®-A53 MCUs are built for industrial applications. These applications include Programmable Logic Controllers (PLCs) and motor drives, which require a unique combination of communications and real-time processing with applications processing. The AM64x combines two instances of the Arm-Based device’s gigabit TSN-enabled PRU-ICSSG with up to two Arm Cortex-A53 cores, up to four Cortex-R5F MCUs, and a Cortex-M4F MCU.

AM64x is architected to provide real-time performance through high-performance R5Fs, configurable SRAM partitioning, Tightly-Coupled Memory banks, and dedicated low-latency paths to and from peripherals for rapid data movement in and out of the SoC. This deterministic architecture allows AM64x to handle the tight control loops in servo drives. At the same time, the peripherals like FSI, GPMC, PWMs, sigma-delta decimation filters, and absolute encoder interfaces help enable several different architectures in these systems.

The Cortex-A53s provide the powerful computing elements necessary for Linux applications. Linux, and Real-time (RT) Linux, is supplied through TI’s Processor SDK Linux, which stays updated to the most current Long Term Support (LTS) Linux kernel, bootloader, and Yocto file system on an annual basis. AM64x helps bridge the Linux world with the real-time world by enabling isolation between Linux applications and real-time streams through configurable memory partitioning. The Cortex-A53s can be assigned to work strictly out of DDR for Linux, and the internal SRAM can be broken up into various sizes for the Cortex-R5Fs to use together or independently.

The Texas Instruments AM64x provides flexible industrial communications capability, including full protocol stacks for EtherCAT SubDevice, EtherNet/IP adapter, PROFINET device, and IO-Link Master. The PRU-ICSSG further provides the ability for gigabit and TSN-based protocols. In addition, the PRU-ICSSG also enables additional interfaces in the SoC, including absolute encoder interfaces and sigma-delta decimation filters.

Functional safety features can be enabled through the integrated Cortex-M4F and dedicated peripherals, which can all be isolated from the rest of the SoC. The AM64x also supports a secure boot.