- support@husseinkey.com

- livechat

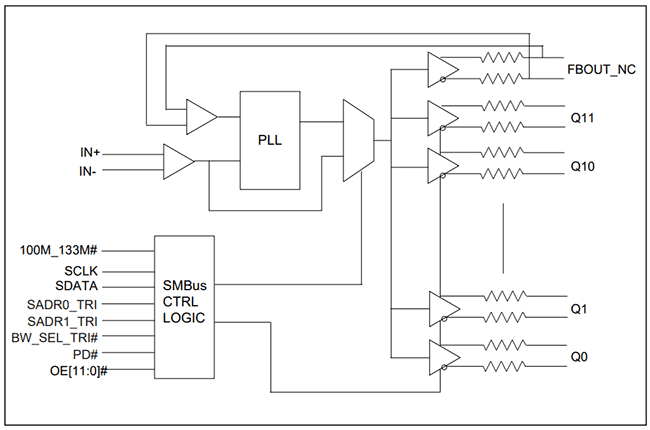

Diodes Incorporated PI6CBE33123 Low-Power PCIe® Clock Buffer is a low-power PCIe 1.0/2.0/3.0/4.0/5.0/6.0 clock buffer. PI6CBE33123 takes a reference input to fan out 12 100MHz low-power differential HCSL outputs with on-chip terminations for 33Ω output impedance. The device supports zero-delay and fanout buffer functions for various applications. An individual OE pin for each output provides easier power management. A proprietary PLL design achieves very low jitter that meets PCIe 1.0/2.0/3.0/4.0/5.0/6.0 requirements. Besides PCIe 100MHz support, this device also supports 133.33MHz via a pin.