- support@husseinkey.com

- livechat

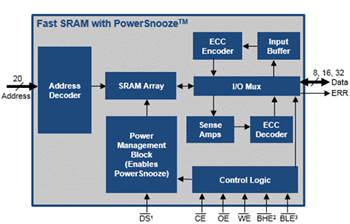

Infineon Technologies MOBL™ Ultra-Reliable Asynchronous SRAMs come with the performance to serve a wide variety of high-reliability industrial, communication, data processing, medical, consumer, and military applications. These SRAMs are available with on-chip ECC. These devices are form-fit-function compatible with older-generation Asynchronous SRAMs. This allows the user to improve system reliability without investing in PCB re-design. These are the first family of devices that combines the access time of Fast Asynchronous SRAM with a unique ultra-low-power sleep mode (PowerSnooze™). These Infineon Technologies Fast SRAMs eliminate the tradeoff between performance and power consumption in Asynchronous SRAM applications. The best features of the existing family of products are achieved through the provision of a novel ultra-low-power sleep mode called PowerSnooze. PowerSnooze is an additional operating mode to standard Asynchronous SRAM operating modes (Active, Standby, and Data-Retention). The Deep Sleep pin (DS#) enables the switching of the device between the high-performance active mode and the ultra-low-power PowerSnooze mode. With a deep sleep current as low as 15 μA on 4-Mbit devices, Fast SRAM with PowerSnooze combines the best features of Fast and Micropower SRAM in a single device.

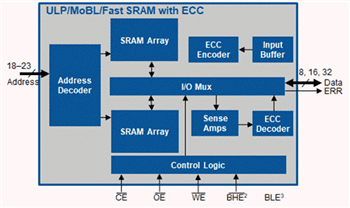

These asynchronous SRAM devices uses (38,32) hamming code ECC for single-bit error detection and correction. The hardware ECC block in these ultra-reliable asynchronous SRAMs performs all ECC-related functions inline, without user intervention. Higher energy extraterrestrial radiation can flip multiple adjacent bits, leading to multi-bit errors. The single-bit error detection and correction capability of the Error Correcting Code are supplemented by a bit-interleaving scheme to prevent the occurrence of multi-bit errors. Together, these features significantly improve Soft Error Rate (SER) performance, resulting in industry-leading FIT rates of less than 0.1 FIT/Mbit.