**WIRELESS & SENSING PRODUCTS**

**Features**

- 2.7-3.6V Input Supply Voltage

- Up to 4 Capacitive Sensor Inputs

- ♦ Patented On-Chip Smart Engine For SAR

- ♦ Capacitance Resolution down to 1aF

- ♦ Capacitance Offset Compensation up to 300pF

- ♦ Multiple thresholds per sensing input

- ♦ Separate configurations per input

- Automatic Calibration

- Up to 2 LED Drivers

- ♦ Up to 20mA Sink Current per IO

- ♦ Intensity Control (256-step PWM)

- Ultra-Low Power Consumption

- ♦ Active Mode: 27 uA

- ♦ Doze Mode: 7 uA

- ♦ Sleep Mode: 1.1 uA

- I2C Serial Interface

- ♦ 2 Sub-Addresses Selectable by Pin

- Programmable Interrupt or Real-Time Status Pin

- -40°C to +85°C Operation

- Compact Size Packages

- ♦ 1.60 x 1.90 mm DFN

- ♦ 1.25 x 1.26 mm WLCSP

- Pb & Halogen Free, RoHS/WEEE compliant

**Applications**

- Mobile Phones

- Tablets

- Notebooks

- Wearables

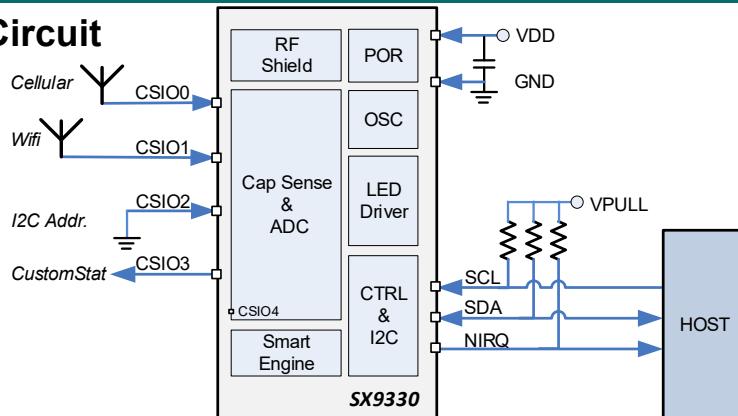

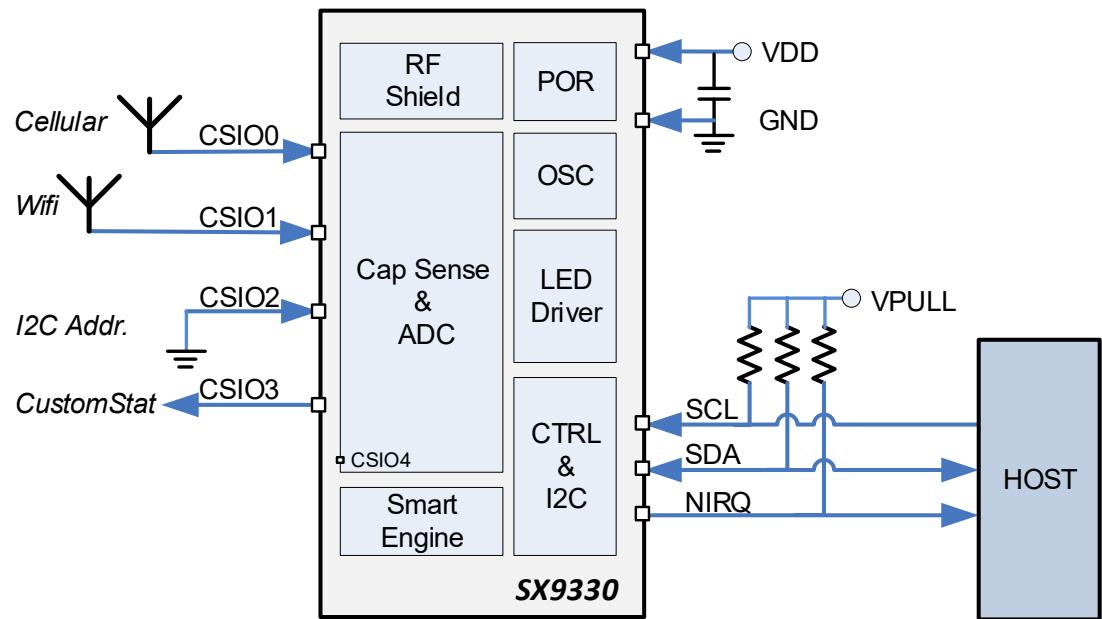

**Typical Application Circuit**

---

## Table of Contents

|                                                        |    |

|--------------------------------------------------------|----|

| 1. General Description.....                            | 5  |

| 1.1. Pin Diagram.....                                  | 5  |

| 1.2. Marking Information.....                          | 6  |

| 1.3. Pin Description .....                             | 7  |

| 2. Electrical Characteristics .....                    | 8  |

| 2.1. Absolute Maximum Ratings.....                     | 8  |

| 2.2. Operating Conditions .....                        | 8  |

| 2.3. Thermal Characteristics .....                     | 8  |

| 2.4. Electrical Specifications .....                   | 9  |

| 3. Proximity Sensing Interface.....                    | 12 |

| 3.1. Introduction.....                                 | 12 |

| 3.2. Scan Period .....                                 | 12 |

| 3.3. Analog Front-End (AFE) .....                      | 13 |

| 3.3.1. Capacitive Sensing Basics .....                 | 13 |

| 3.3.2. AFE Block-Diagram .....                         | 15 |

| 3.3.3. Capacitance-to-Voltage Conversion (C-to-V)..... | 15 |

| 3.3.4. Shield Control .....                            | 15 |

| 3.3.5. Offset Compensation.....                        | 15 |

| 3.3.6. Analog-to-Digital Conversion (ADC) .....        | 16 |

| 3.4. Digital Processing .....                          | 16 |

| 3.4.1. Overview .....                                  | 16 |

| 3.4.2. PROXADC Update .....                            | 18 |

| 3.4.3. PROXUSEFUL Update .....                         | 19 |

| 3.4.4. PROXAVG Update .....                            | 20 |

| 3.4.5. PROXDIFF Update .....                           | 20 |

| 3.4.6. PROXSTAT Update .....                           | 21 |

| 3.5. Host Operation .....                              | 22 |

| 3.6. Operational Modes.....                            | 23 |

| 3.6.1. Active .....                                    | 23 |

| 3.6.2. Doze .....                                      | 23 |

---

|                                                   |    |

|---------------------------------------------------|----|

| 3.6.3. Sleep .....                                | 23 |

| 4. I2C Interface .....                            | 24 |

| 4.1. Introduction.....                            | 24 |

| 4.2. I2C Read/Write Format.....                   | 24 |

| 5. Reset.....                                     | 25 |

| 5.1. Power-Up.....                                | 25 |

| 5.2. Software Reset .....                         | 25 |

| 6. Interrupt.....                                 | 26 |

| 6.1. Assertion and Clearing .....                 | 26 |

| 7. Registers .....                                | 27 |

| 8. Application Information .....                  | 52 |

| 8.1. Typical Application Circuit.....             | 52 |

| 8.2. External Components Recommended Values ..... | 52 |

| 9. Packaging Information.....                     | 53 |

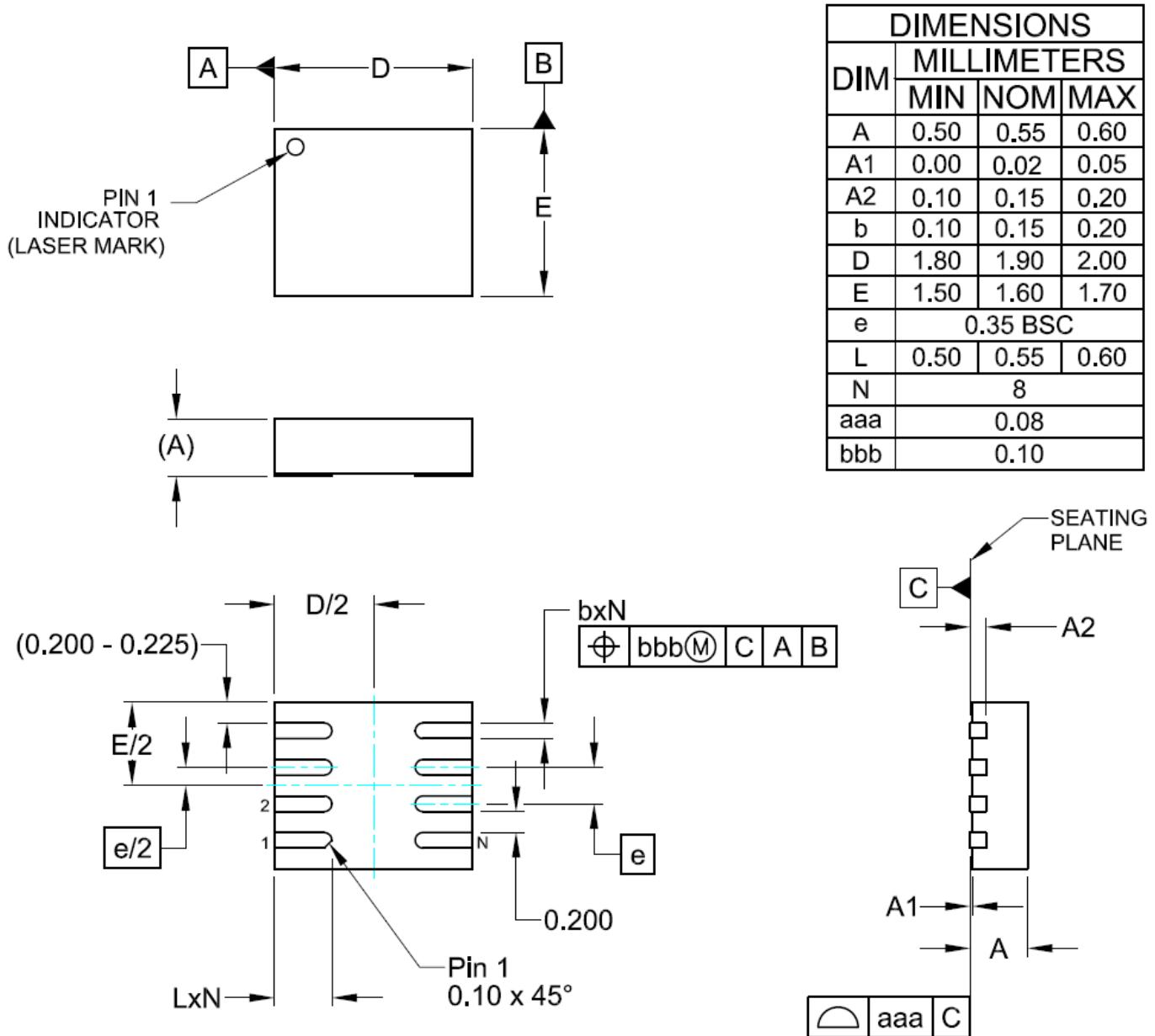

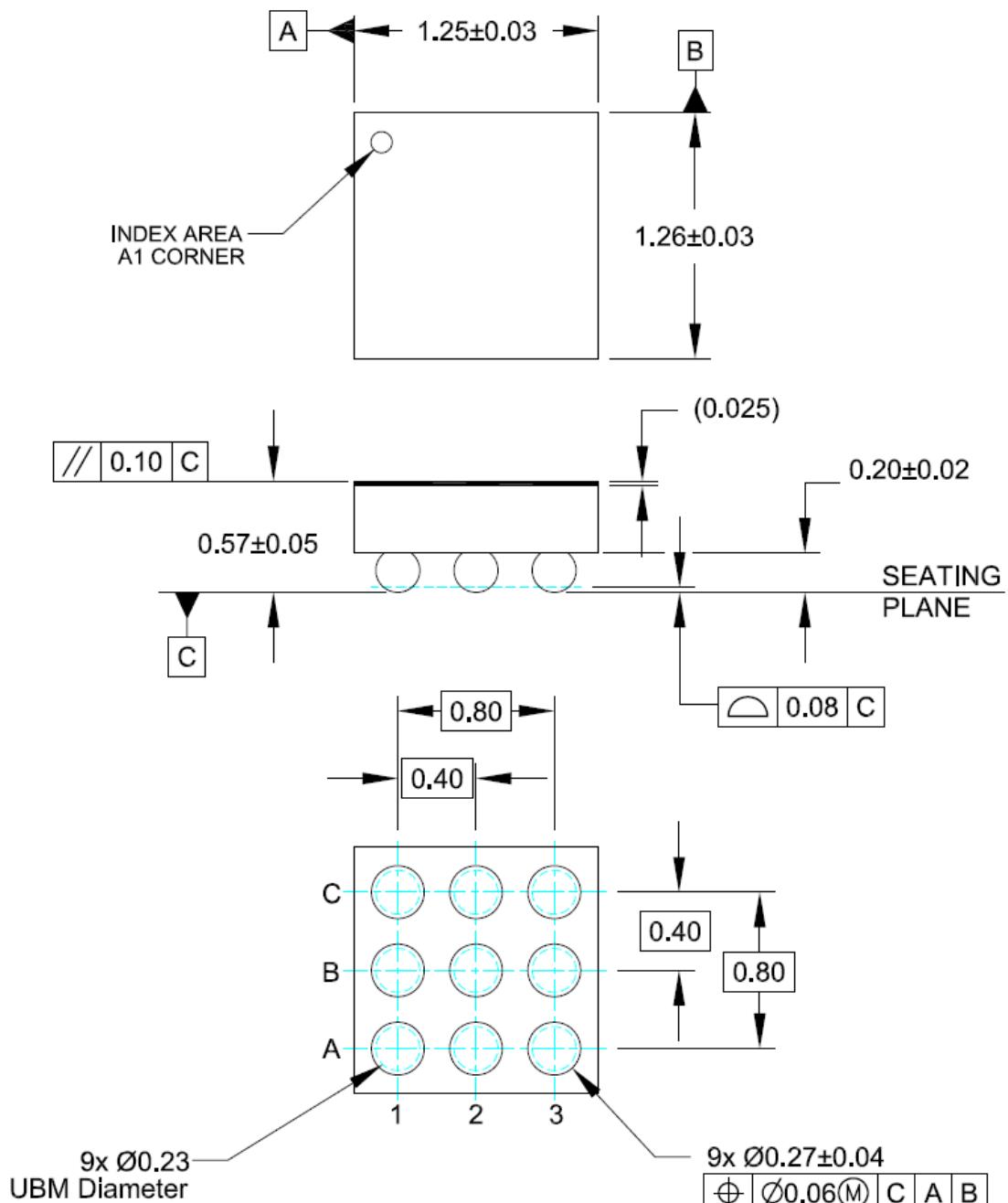

| 9.1. Outline Drawing .....                        | 53 |

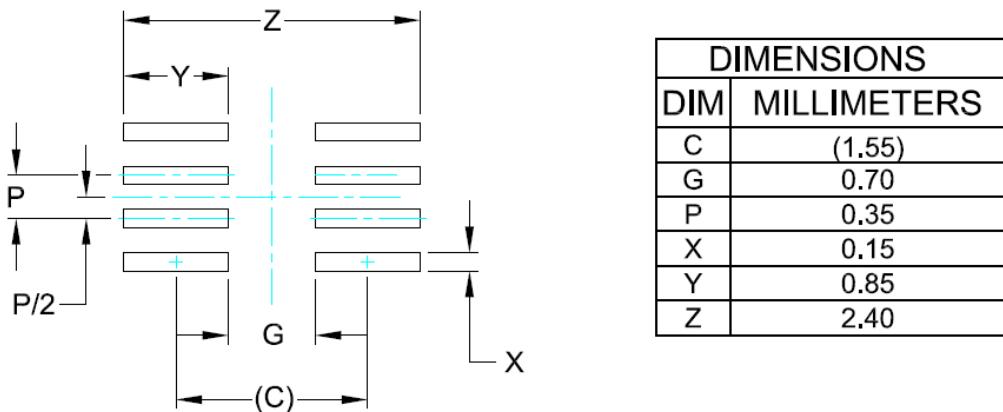

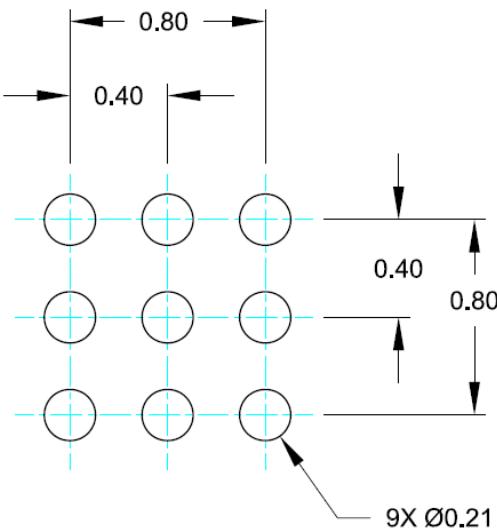

| 9.2. Land Pattern .....                           | 55 |

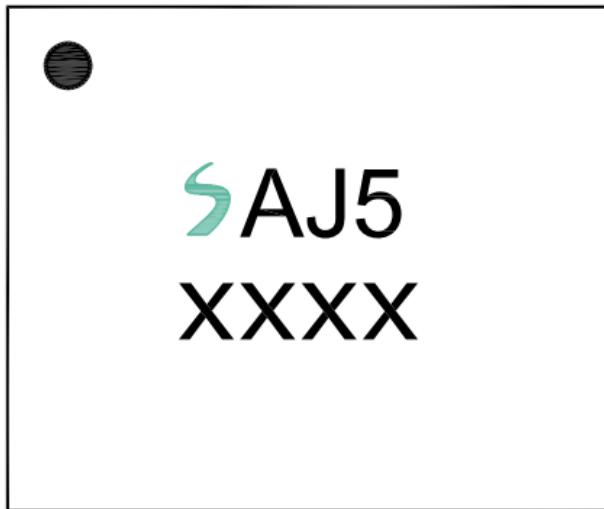

## Ordering Information

| Part Number               | Package             | Marking |

|---------------------------|---------------------|---------|

| SX9330IULTRT <sup>1</sup> | DFN-8               | AJ5     |

| SX9330ICSTRT <sup>1</sup> | WLCSP-9             | RM2     |

| SX9330EVKA                | Eval. Kit for DFN   | -       |

| SX9330EVKB                | Eval. Kit for WLCSP | -       |

<sup>1</sup> 3000 Units/reel

*Table 1: Ordering Information*

# 1. General Description

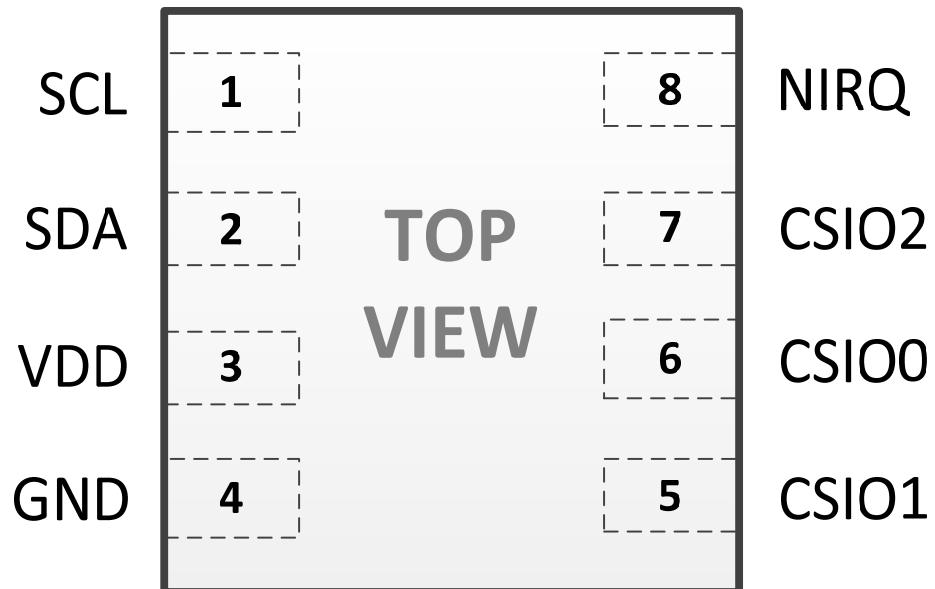

## 1.1. Pin Diagram

Figure 1: Pin Diagram – DFN Package

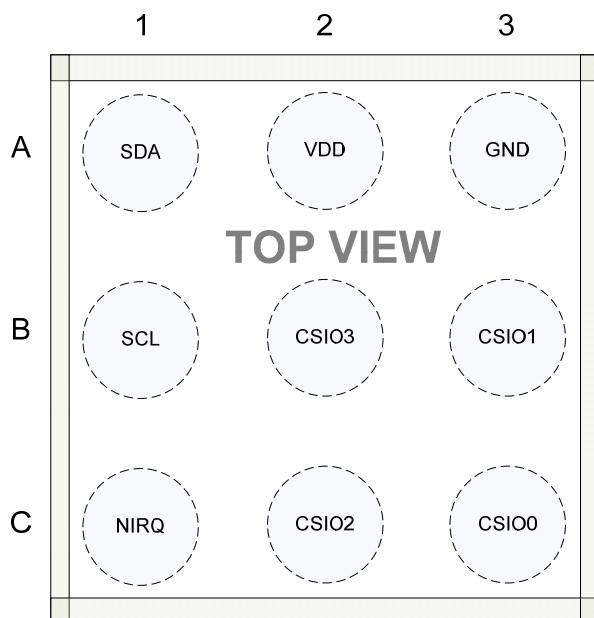

Figure 2: Pin Diagram – WLCSP Package

---

## 1.2. Marking Information

xxxx = Lot Number

*Figure 3: Marking Information – DFN Package*

xxxx = Lot Number

*Figure 4: Marking Information – WLCSP Package*

## 1.3. Pin Description

| Name    | Type                 | Description                                                                             |

|---------|----------------------|-----------------------------------------------------------------------------------------|

| VDD     | Power                | Power Supply, requires decoupling capacitor.                                            |

| GND     | Ground               | Ground.                                                                                 |

| CSIO0   | Analog/Digital       | Capacitive Sensor Input/Shield OR Digital I/O OR Analog Input.                          |

| CSIO1   | Analog/Digital       | Capacitive Sensor Input/Shield OR Digital I/O OR Analog Input.                          |

| CSIO2   | Analog/Digital       | Capacitive Sensor Input/Shield OR Digital I/O OR Analog Input OR I2C Sub-Address Input. |

| CSIO3*  | Analog/Digital       | Capacitive Sensor Input/Shield OR Digital I/O OR Analog Input.                          |

| CSIO4** | Analog/Digital       | Capacitive Sensor Input/Shield OR Digital I/O OR Analog Input.                          |

| SCL     | Digital Input        | I2C Clock, requires pull-up resistor.                                                   |

| SDA     | Digital Input/Output | I2C Data, requires pull-up resistor.                                                    |

| NIRQ    | Digital Input/Output | Interrupt Output OR Digital Input/Output, requires pull-up resistor.                    |

\* Not bonded-out in DFN package.

\*\* Not balled/bonded-out both in DFN and WLCSP packages.

**Table 2: Pin Description**

## 2. Electrical Characteristics

### 2.1. Absolute Maximum Ratings

Stresses above the values listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these, or any other conditions beyond the "Operating Conditions", is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability and proper functionality.

| Parameter                               | Symbol             | Min                    | Max | Unit |

|-----------------------------------------|--------------------|------------------------|-----|------|

| Supply Voltage                          | V <sub>DD</sub>    | -0.5                   | 3.9 | V    |

| Input Voltage (non-supply pins)         | V <sub>IN</sub>    | -0.5                   | 3.9 |      |

| Input Current Per Pin (non-supply pins) | I <sub>IN</sub>    | -50                    | 50  | mA   |

| Total Input Current (non-supply pins)   | I <sub>INTOT</sub> | -300                   | 300 |      |

| Operating Junction Temperature          | T <sub>JCT</sub>   | -40                    | 125 | °C   |

| Reflow Temperature                      | T <sub>RE</sub>    | -                      | 260 |      |

| Storage Temperature                     | T <sub>STOR</sub>  | -50                    | 150 |      |

| ESD CDM                                 | ESD <sub>CDM</sub> | 1                      | -   | kV   |

| ESD HBM (ANSI/ESDA/JEDEC JS-001)        | CSIOx pins         | ESD <sub>HBMCSIO</sub> | 8   | kV   |

|                                         | Other pins         | ESD <sub>HBMOTH</sub>  | 4   |      |

Table 3: Absolute Maximum Ratings

### 2.2. Operating Conditions

| Parameter           | Symbol            | Min | Max | Unit |

|---------------------|-------------------|-----|-----|------|

| Supply Voltage      | V <sub>DD</sub>   | 2.7 | 3.6 | V    |

| Pull-up Voltage     | V <sub>PULL</sub> | 1.6 | 3.6 | V    |

| Ambient Temperature | T <sub>A</sub>    | -40 | 85  | °C   |

Table 4: Operating Conditions

Note: V<sub>DD</sub> and V<sub>PULL</sub> (on SCL/SDA/NIRQ) are fully independent, i.e. can be turned ON/OFF separately and in any sequence without creating any leakage current.

### 2.3. Thermal Characteristics

| Parameter                                                     | Symbol             | Typical | Unit |

|---------------------------------------------------------------|--------------------|---------|------|

| Thermal Resistance - Junction to Air (Static Airflow) - DFN   | θ <sub>JADFN</sub> | 203     | °C/W |

| Thermal Resistance - Junction to Air (Static Airflow) - WLCSP | θ <sub>JACSP</sub> | 120     | °C/W |

Table 5: Thermal Characteristics

Note: θ<sub>JA</sub> is calculated from a package in still air, mounted to 3" x 4.5", 4-layer FR4 PCB per JESD51 standards.

## 2.4. Electrical Specifications

All values are valid within the full operating conditions unless otherwise specified.

Typical values are given for  $T_A = +25^\circ\text{C}$ ,  $VDD=3.3\text{V}$  unless otherwise specified.

| Parameter                                                | Symbol           | Conditions                                                                                                                                                              | Min           | Typ.      | Max   | Unit       |

|----------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|-------|------------|

| <b>Current Consumption</b>                               |                  |                                                                                                                                                                         |               |           |       |            |

| Sleep                                                    | $I_{SLEEP}$      | Power down.<br>PHEN = 000000 or chip paused.<br>PWM OFF. I2C listening.                                                                                                 | -             | 1.1       | 5     | uA         |

| Doze                                                     | $I_{DOZE}$       | SCANPERIOD = hC8 (~400ms)<br>FREQ = b00110 (~100kHz)<br>RESOLUTION = 64<br>PHEN = 00001<br>ADC filt. and Adv. features/engines OFF.<br>PWM OFF. I2C listening. No load. | -             | 7         | 15    |            |

| Active                                                   | $I_{ACTIVE}$     | SCANPERIOD = h0F (~30ms)<br>FREQ = b00110 (~100kHz)<br>RESOLUTION = 64<br>PHEN = 00001<br>ADC filt. and Adv. features/engines OFF.<br>PWM OFF. I2C listening. No load.  | -             | 27        | 48    |            |

| <b>Capacitive Sensing Interface</b>                      |                  |                                                                                                                                                                         |               |           |       |            |

| Measurement Range<br>(Unit Capacitor, Cf. AGAIN)         | $C_{RANGEUNIT}$  |                                                                                                                                                                         | -             | +/-0.55   | -     | pF         |

| Measurement Resolution                                   | $N_{BIT}$        |                                                                                                                                                                         | -             | 21        | -     | bits       |

|                                                          | $C_{RES}$        | AGAIN = 0001                                                                                                                                                            | -             | 1         | -     | aF         |

| Nominal Oscillator Frequency                             | $F_{Osc}$        |                                                                                                                                                                         | -             | 4         | -     | MHz        |

| Oscillator Trim Accuracy                                 | $F_{Trim}$       | Around Nominal Value.<br>$T_A = +25^\circ\text{C}$ , $VDD = 3.3\text{V}$ .                                                                                              | -4            | -         | +4    | %          |

| Oscillator Temp. Dependency                              | $F_{Temp}$       | Around Trim Result.<br>Full $T_A$ range, $VDD = 3.3\text{V}$ .                                                                                                          | -             | +/-1      | -     | %          |

| Oscillator VDD Dependency                                | $F_{VDD}$        | Around Trim Result.<br>$T_A = +25^\circ\text{C}$ , Full VDD range.                                                                                                      | -             | +/-0.6    | -     | %          |

| Nominal Sampling Frequencies                             | $F_s$            | Programmable with FREQ                                                                                                                                                  | $F_{Osc}/864$ | -         | 250   | kHz        |

| External DC Cap. to Ground per Measurement Phase         | $C_{DCEXT}$      | One CSIOx as measured input.                                                                                                                                            | -             | -         | 300   | pF         |

| External Series Resistor per CSIOx Pin                   | $R_{SEREXT}$     |                                                                                                                                                                         | -             | -         | 2     | k $\Omega$ |

| Pre-Charge Input Resistor<br>(Unit Value, Cf. RESFILTIN) | $R_{FILTINUNIT}$ |                                                                                                                                                                         | -             | 2         | -     | k $\Omega$ |

| Compensation Resistor                                    | $R_{INTUNIT}$    |                                                                                                                                                                         | -             | 125       | -     | $\Omega$   |

| <b>External Input Voltage Conversion</b>                 |                  |                                                                                                                                                                         |               |           |       |            |

| Input Range                                              | $V_{INRANGE}$    | CSIOx pin                                                                                                                                                               | 0             | -         | VDD   | V          |

| Output Range                                             | $V_{OUTRANGE}$   | PROXUSEFUL                                                                                                                                                              | 0             | -         | 32767 | LSB        |

| Output Slope                                             | $V_{OUTSLOPE}$   | PROXUSEFUL                                                                                                                                                              | -             | 32768/VDD | -     | LSB/V      |

| Parameter                                                 | Symbol                | Conditions                                                                                                            | Min                   | Typ.                 | Max                  | Unit   |

|-----------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|----------------------|--------|

| <b>Internal Temperature Sensor Conversion</b>             |                       |                                                                                                                       |                       |                      |                      |        |

| Input Range                                               | TINRANGE              | Ambient Temperature (TA)                                                                                              | -40                   | -                    | 85                   | °C     |

| Output Range                                              | TOUSTRANGE            | PROXUSEFUL                                                                                                            | 0                     | -                    | 32767                | LSB    |

| Output Slope                                              | TOUTSLOPE             | PROXUSEFUL                                                                                                            | -                     | 58                   | -                    | LSB/°C |

| <b>Digital Input/Output: SCL, SDA, NIRQ, CSIOx</b>        |                       |                                                                                                                       |                       |                      |                      |        |

| Input High Voltage                                        | VIHCSIO               |                                                                                                                       | 0.7*V <sub>PULL</sub> | -                    | VDD+0.3 <sup>1</sup> | V      |

|                                                           | VIHI2CNIRQ            |                                                                                                                       | 0.7*V <sub>PULL</sub> | -                    | 3.6                  |        |

| Input Low Voltage                                         | V <sub>IL</sub>       |                                                                                                                       | -0.5                  | -                    | 0.45                 |        |

| Input Leakage Current                                     | I <sub>IL</sub>       |                                                                                                                       | -1                    | -                    | 1                    | uA     |

| Input Hysteresis                                          | V <sub>HYS</sub>      |                                                                                                                       | 0.035                 | 0.15                 | -                    | V      |

| Output Low Current (SDA)                                  | I <sub>OL04</sub>     | V <sub>O</sub> L ≤ 0.32V                                                                                              | 3                     | -                    | -                    | mA     |

|                                                           | I <sub>OL06</sub>     | V <sub>O</sub> L ≤ 0.6V                                                                                               | 6                     | -                    | -                    |        |

| Output Low Voltage (NIRQ, CSIOx)                          | V <sub>OL20</sub>     | I <sub>O</sub> L = 20mA, VDD = 3.3V                                                                                   | -                     | 0.4                  | 1                    | V      |

|                                                           | V <sub>OL10</sub>     | I <sub>O</sub> L = 10mA, VDD = 3.3V                                                                                   | -                     | 0.2                  | 0.5                  | V      |

|                                                           | V <sub>OL5</sub>      | I <sub>O</sub> L = 5mA, VDD = 3.3V                                                                                    | -                     | 0.1                  | 0.2                  | V      |

| Output High Voltage (open-drain mode)                     | V <sub>OHCSIO</sub>   | From external pull-up or LED.                                                                                         | -                     | -                    | VDD+0.3 <sup>1</sup> | V      |

|                                                           | V <sub>OHNIRQ</sub>   |                                                                                                                       | -                     | -                    | 3.6                  | V      |

| Output High Current (push-pull mode)                      | I <sub>OHCSIO</sub>   | V <sub>O</sub> H ≥ VDD - 0.4V                                                                                         | 3                     | -                    | -                    | mA     |

| CSIO2 external pull-down resistance. (Alternate I2C addr) | R <sub>LOWCSIO2</sub> |                                                                                                                       | -                     | 0                    | 500                  | Ω      |

| Slew Rate (CSIOx both edges, NIRQ falling edge only)      | SR <sub>00</sub>      | 30-70%, 100pF load<br>SLEWRATE=00/01/10/11<br>respectively.                                                           | -                     | 2                    | -                    | ns     |

|                                                           | SR <sub>01</sub>      |                                                                                                                       | -                     | 18                   | -                    |        |

|                                                           | SR <sub>10</sub>      |                                                                                                                       | -                     | 32                   | -                    |        |

|                                                           | SR <sub>11</sub>      |                                                                                                                       | -                     | 56                   | -                    |        |

| <b>Miscellaneous</b>                                      |                       |                                                                                                                       |                       |                      |                      |        |

| Power-up Time                                             | T <sub>POR</sub>      |                                                                                                                       | -                     | -                    | 5                    | ms     |

| Unpause Time                                              | T <sub>UNPAUSEC</sub> | Through unpause Command.<br>From SCL rising edge on bit0 of register RegCmd to PAUSESTAT falling edge.                | -                     | 171/F <sub>Osc</sub> | -                    | us     |

|                                                           | T <sub>UNPAUSEI</sub> | Through Interrupt clearing.<br>From SCL rising edge on bit0 of slave address after restart to PAUSESTAT falling edge. | -                     | 60/F <sub>Osc</sub>  | -                    |        |

<sup>1</sup> Without exceeding 3.6V

**Table 6: Electrical Specifications**

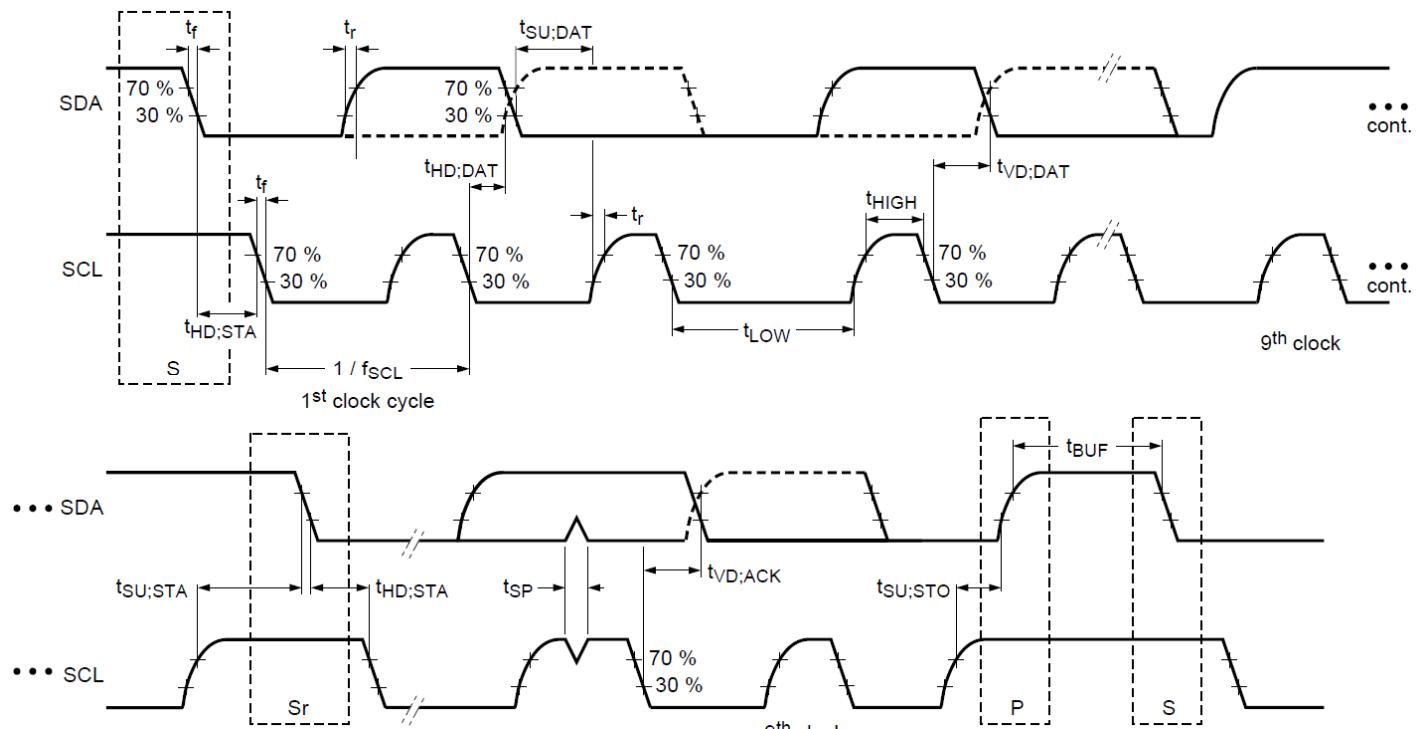

| Parameter                                           | Symbol       | Conditions               | Min                  | Typ. | Max | Unit |

|-----------------------------------------------------|--------------|--------------------------|----------------------|------|-----|------|

| <b>I2C Timing Specifications (Cf. figure below)</b> |              |                          |                      |      |     |      |

| SCL clock frequency                                 | $f_{SCL}$    |                          | -                    | -    | 400 | kHz  |

| SCL low period                                      | $t_{LOW}$    |                          | 1.3                  | -    | -   |      |

| SCL high period                                     | $t_{HIGH}$   |                          | 0.6                  | -    | -   |      |

| Data setup time                                     | $t_{SU;DAT}$ |                          | 0.1                  | -    | -   |      |

| Data hold time                                      | $t_{HD;DAT}$ |                          | 0                    | -    | -   |      |

| Repeated start setup time                           | $t_{SU;STA}$ |                          | 0.6                  | -    | -   |      |

| Start condition hold time                           | $t_{HD;STA}$ |                          | 0.6                  | -    | -   | us   |

| Stop condition setup time                           | $t_{SU;STO}$ |                          | 0.6                  | -    | -   |      |

| Bus free time between stop and start                | $t_{BUF}$    |                          | 1.3                  | -    | -   |      |

| Data valid time                                     | $t_{VD;DAT}$ |                          | -                    | -    | 0.9 |      |

| Data valid acknowledge time                         | $t_{VD;ACK}$ |                          | -                    | -    | 0.9 |      |

| Rise time of SCL and SDA                            | $t_{R400}$   | Load $\leq 400\text{pF}$ | 20                   | -    | 300 | ns   |

| Fall time of SCL and SDA                            | $t_{F400}$   | Load $\leq 400\text{pF}$ | $20^*(V_{PULL}/5.5)$ | -    | 300 | ns   |

| Input glitch suppression                            | $t_{SP}$     | Note 1                   | -                    | -    | 50  | ns   |

Note 1: Minimum glitch amplitude is  $0.7V_{DD}$  at High level and Maximum  $0.3V_{DD}$  at Low level.

**Table 7: I2C Timing Specifications**

**Figure 5: I2C Timing**

# 3. Proximity Sensing Interface

## 3.1. Introduction

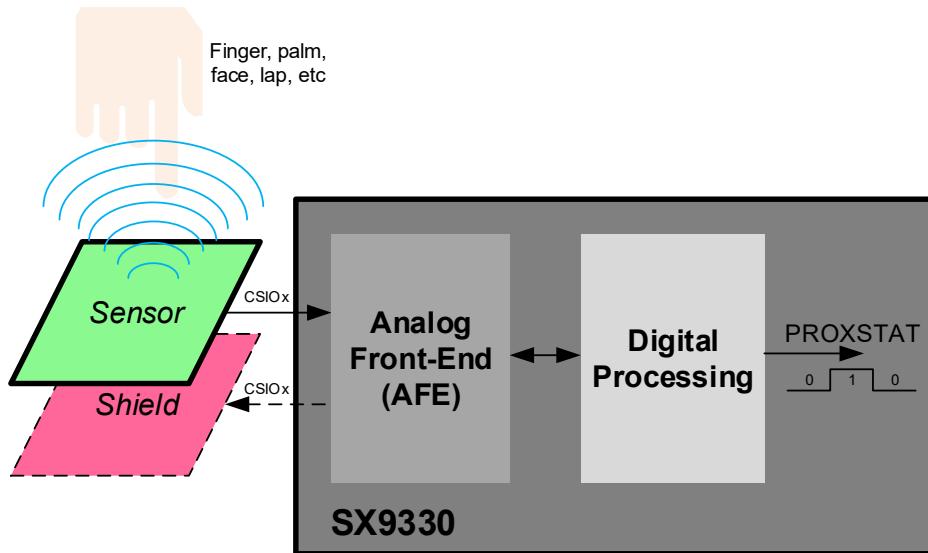

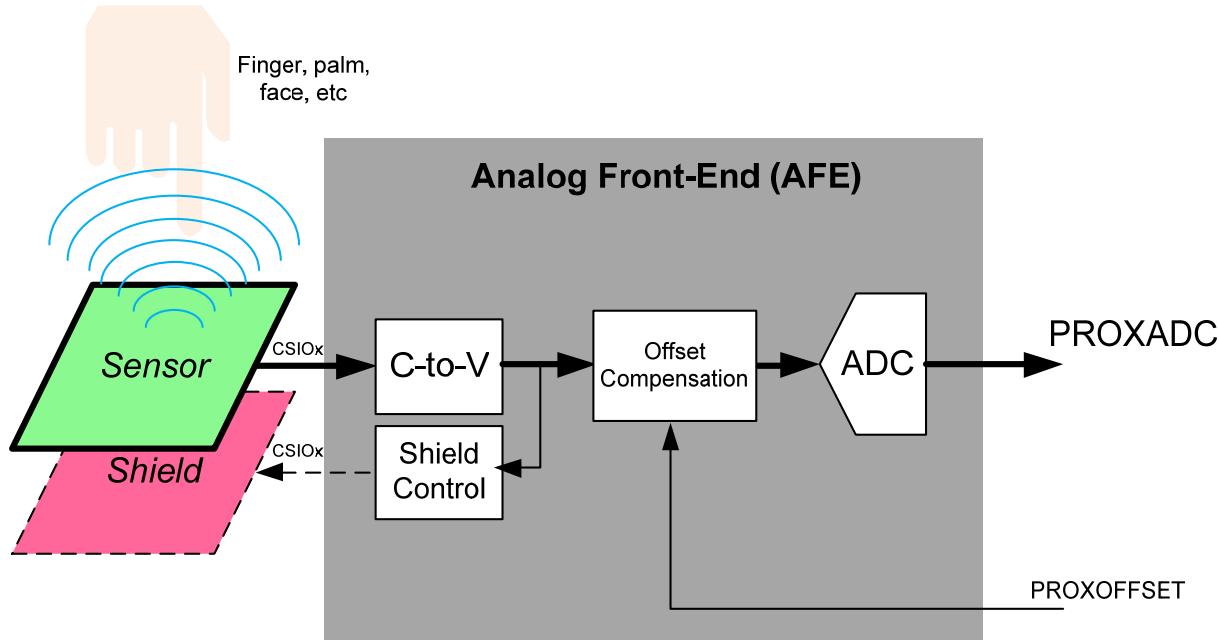

The purpose of the proximity sensing interface is to detect when a conductive object (usually a body part i.e. finger, palm, face, etc) is in the proximity of the system. Note that proximity sensing can be done through the air or through a solid (typically plastic) overlay (also called “touch” sensing).

The chip's proximity sensing interface is based on capacitive sensing technology. An overview is given in figure below.

Figure 6: Proximity Sensing Interface Overview

- ❖ The sensor can be a simple copper area on a PCB or FPC for example. Its capacitance (to ground) will vary when a conductive object is moving in its proximity.

- ❖ The optional shield can also be a simple copper area on a PCB or FPC below/under/around the sensor. It is used to protect the sensor against potential surrounding noise sources and improve its global performance. It also brings directivity to the sensing, for example sensing objects approaching from top only.

- ❖ The analog front-end (AFE) performs the raw sensor's capacitance measurement and converts it into a digital value. It also controls the shield.

- ❖ The digital processing block computes the raw capacitance measurement from the AFE and extracts a binary information PROXSTAT corresponding to the proximity status, i.e. object is “Far” or “Close”. It also triggers AFE operations (compensation, etc).

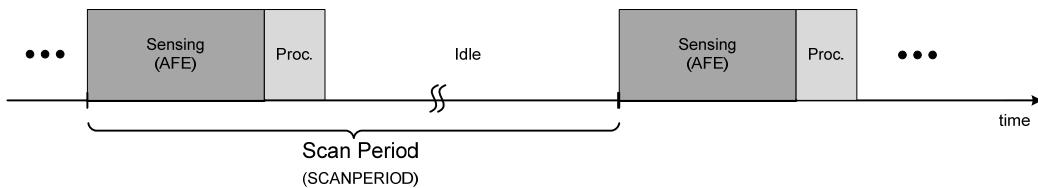

## 3.2. Scan Period

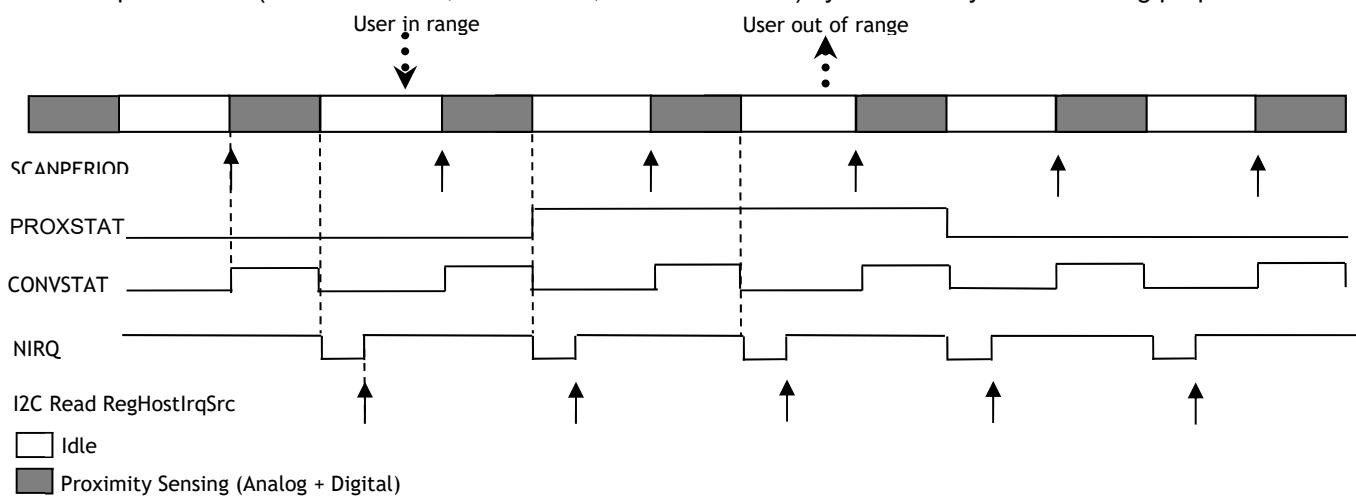

To save power and since the proximity event is slow by nature, the chip will awake regularly at a programmed scan period (SCANPERIOD) to first sense sequentially each of the enabled phases (PHEN) and then process new proximity samples/info. The chip will then return to an idle mode for the rest of the scan period as illustrated in the figure below.

**Figure 7: Proximity Sensing Sequencing**

The sensing and processing durations vary with the number of phases enabled, the sampling frequency, the resolution programmed, etc. During the Idle state, the chip's analog circuits are turned off. Upon expiry of the idle timer, a new scan period cycle begins.

The scan period determines the minimum reaction time (actual/final reaction time also depends on debounce and filtering settings) and can be programmed from typ. 2ms to 4s.

### 3.3. Analog Front-End (AFE)

#### 3.3.1. Capacitive Sensing Basics

Capacitive sensing is the art of measuring a small variation of capacitance in a noisy environment. As mentioned above, the chip's proximity sensing interface is based on capacitive sensing technology. In order to illustrate some of the user choices and compromises required when using this technology it is useful to understand its basic principles.

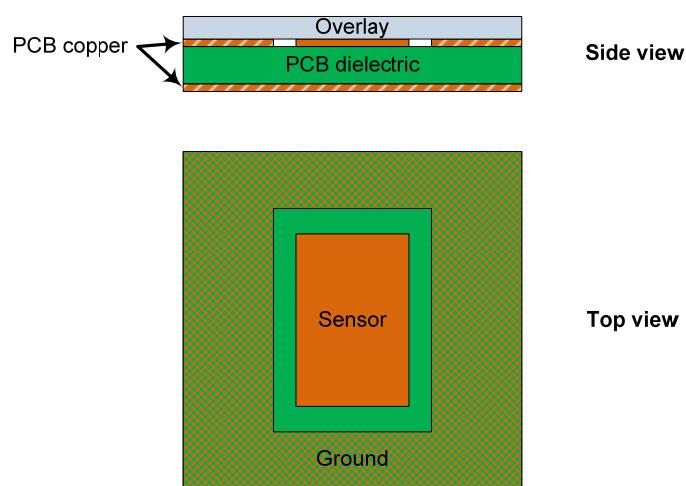

To illustrate the principle of capacitive sensing we will use the simplest implementation where the sensor is a copper plate on a PCB.

The figure below shows a cross-section and top view of a typical capacitive sensing implementation. The sensor connected to the chip is a simple copper area on top layer of the PCB. It is usually surrounded (shielded) by ground for noise immunity (shield function) but also indirectly couples via the ground areas of the rest of the system (PCB ground traces/planes, housing, etc). For obvious reasons (design, isolation, robustness ...) the sensor is stacked behind an overlay which is usually integrated in the housing of the complete system.

**Figure 8: Typical Capacitive Sensing Implementation**

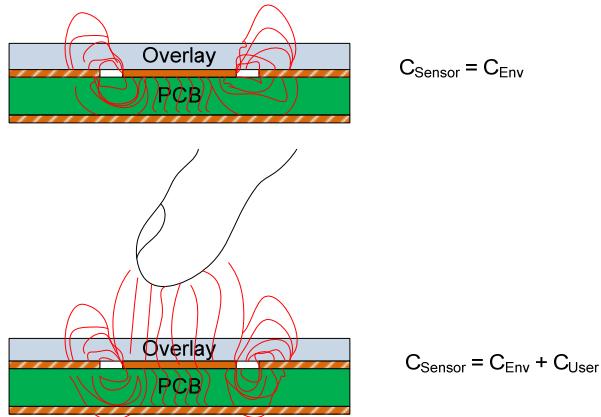

When the conductive object to be detected (finger/palm/face, etc) is not present, the sensor only sees an inherent capacitance value  $C_{Env}$  created by its electrical field's interaction with the environment, in particular with ground areas.

When the conductive object (finger/palm/face, etc) approaches, the electrical field around the sensor will be modified and the total capacitance seen by the sensor increased by the user capacitance  $C_{User}$ . This phenomenon is illustrated in the figure below.

**Figure 9: Proximity Effect on Electrical Field and Sensor Capacitance**

The challenge of capacitive sensing is to detect this relatively small variation of  $C_{Sensor}$  ( $C_{User}$  usually contributes for a few percent only) and differentiate it from environmental noise ( $C_{Env}$  also slowly varies together with the environment characteristics like temperature, etc). For this purpose, the chip integrates an auto offset compensation mechanism which dynamically monitors and removes the  $C_{Env}$  component to extract and process  $C_{User}$  only.

In first order,  $C_{User}$  can be estimated by the formula below:

$$C_{User} = \frac{\epsilon_0 \cdot \epsilon_r \cdot A}{d}$$

$A$  is the common area between the two electrodes hence the common area between the user's finger/palm/face and the sensor.

$d$  is the distance between the two electrodes hence the proximity distance between the user and the system.

$\epsilon_0$  is the free space permittivity and is equal to  $8.85 \cdot 10^{-12} \text{ F/m}$  (constant)

$\epsilon_r$  is the dielectric relative permittivity.

Typical permittivity of some common materials is given in the table below.

| Material      | Typical $\epsilon_r$ |

|---------------|----------------------|

| Glass         | 8                    |

| FR4           | 5                    |

| Acrylic Glass | 3                    |

| Wood          | 2                    |

| Air           | 1                    |

**Table 8: Typical Permittivity of Some Common Materials**

From the discussions above we can conclude that the most robust and efficient design will be the one that minimizes  $C_{Env}$  value and variations while improving  $C_{User}$ .

### 3.3.2. AFE Block-Diagram

Figure 10: Analog Front-End Block Diagram

### 3.3.3. Capacitance-to-Voltage Conversion (C-to-V)

The sensitivity of the interface is determined mainly by the AGAIN parameter.

FREQ defines the operating frequency of the interface.

### 3.3.4. Shield Control

When not being measured, any CSIOx pin can be used as a shield.

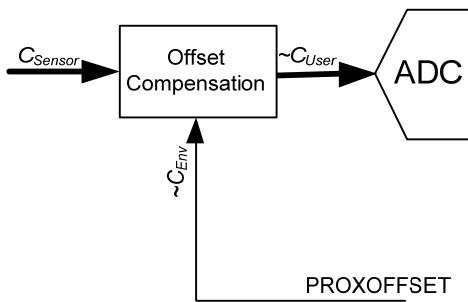

### 3.3.5. Offset Compensation

Offset compensation consists of performing a one-time measurement of  $C_{Env}$  and subtracting it from the total capacitance  $C_{Sensor}$  in order to feed the ADC with the closest contribution of  $C_{User}$  only.

Figure 11: Offset Compensation Block Diagram

The ADC input  $C_{User}$  is the total capacitance  $C_{Sensor}$  to which  $C_{Env}$  is subtracted.

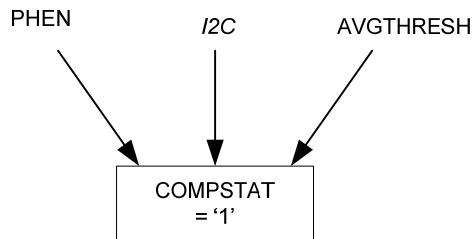

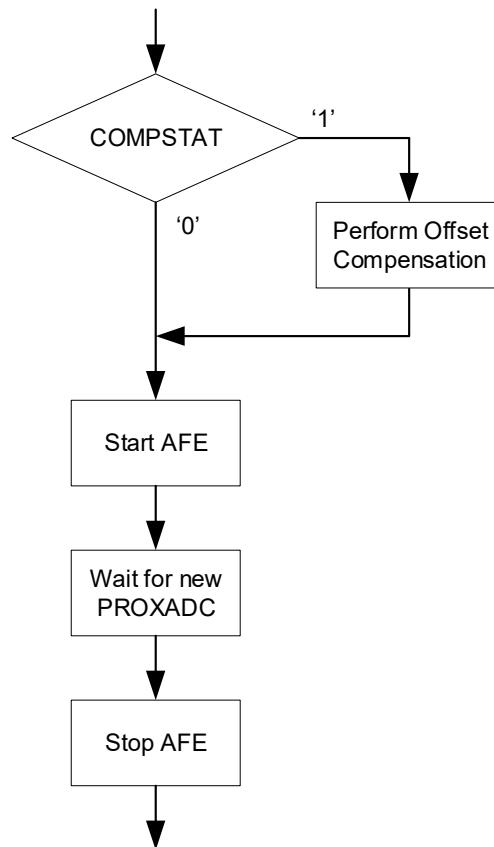

There are three main compensation sources which are illustrated in the figure below. When set to 1, COMPSTAT will only be reset once the compensation is completed.

**Figure 12: Main Compensation Request Sources**

- PHEN: a compensation is automatically requested for a measurement phase on the rising edge of its PHEN bit (needs extra activation command if all PHEN were set to 0).

- I2C: a compensation for one or more phases (enabled thru COMPEN) can be manually requested anytime by the host through I2C interface by issuing the compensation command.

- AVGTHRESH: a compensation for the relevant phase only (or for all, depending on AVGCOMPETHOD), can be automatically requested if it is detected that  $C_{Env}$  has drifted beyond a predefined range programmed by the host.

Note that when compensation occurs, PROXDIFF is reset and hence all compensated phases' PROXSTAT flags turn OFF (i.e. no proximity detected) independently from the user's potential actual presence (except if start-up detection is enabled).

### 3.3.6. Analog-to-Digital Conversion (ADC)

An ADC is used to convert the analog capacitance information into a digital word PROXADC.

## 3.4. Digital Processing

### 3.4.1. Overview

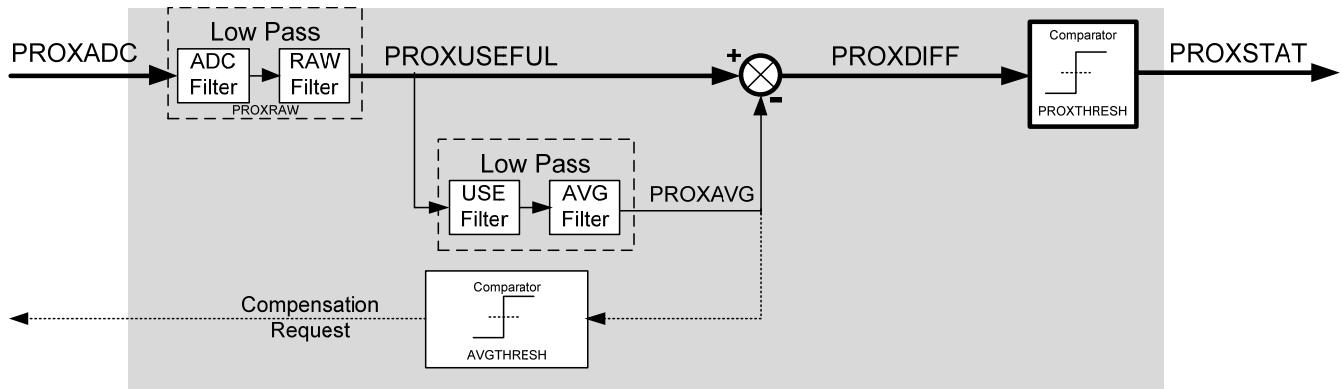

The main purpose of the digital processing block is to convert the raw capacitance information coming from the AFE (PROXADC) into a robust and reliable digital flag (PROXSTAT) indicating if something is within range of the proximity sensor(s).

The offset compensation performed in the AFE is a one-time measurement. However, the environment capacitance  $C_{Env}$  may vary with time (temperature, nearby objects, etc). Hence, in order to get the best estimation of  $C_{User}$  (PROXDIFF), the digital processing block dynamically tracks and subtracts  $C_{Env}$  variations. This is performed by filtering PROXUSEFUL to extract its slow variations (PROXAVG).

PROXDIFF is compared to the user programmable threshold (PROXTHRESH) to extract PROXSTAT flag.

**Figure 13: Digital Processing Block Diagram**

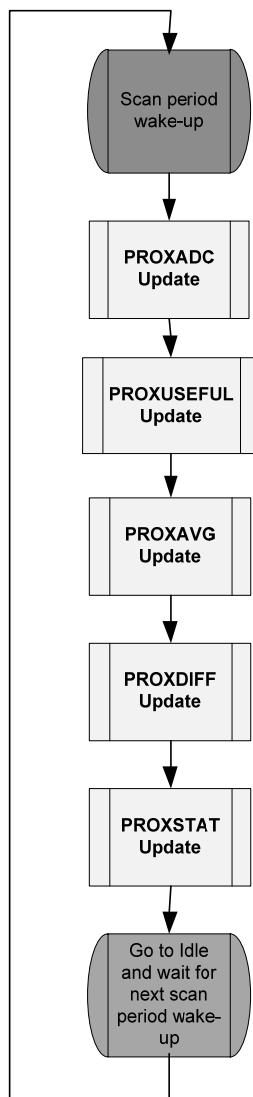

The digital processor sequence (for all enabled phases) is illustrated below. At every scan period wake-up, the block updates sequentially PROXADC, PROXUSEFUL, PROXAVG, PROXDIF and PROXSTAT before going back to Idle mode.

**Figure 14: Digital Processor Sequence**

The digital processing block also updates COMPSTAT (set when compensation is currently pending execution or completion).

### 3.4.2. PROXADC Update

PROXADC update consists mainly of starting the AFE and waiting for the new PROXADC values (one for each phase) to be ready. If compensation was pending it is performed first.

**Figure 15: PROXADC Update**

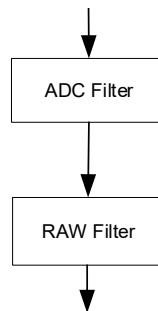

Note that PROXADC is not available in the “Main Data Readback” section of the registers. If needed, it can be observed by reading PROXUSEFUL while both ADC and RAW filters are disabled.

### 3.4.3. PROXUSEFUL Update

PROXUSEFUL update consists of filtering PROXADC, using both ADC and RAW filters, to remove its high frequencies components (system noise, interferer, etc) and extract only user activity (few Hz max) and slow environment changes.

**Figure 16: PROXUSEFUL Update**

Please refer to the application notes for further details.

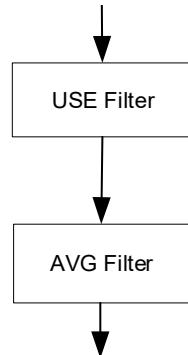

### 3.4.4. PROXAVG Update

PROXAVG update consists of averaging PROXUSEFUL, using both USE and AVG filters, to ignore its “fast” variations (i.e. user finger/palm/hand) and extract only the very slow variations of environment capacitance  $C_{Env}$ .

**Figure 17: PROXAVG Update**

Please refer to the application notes for further details.

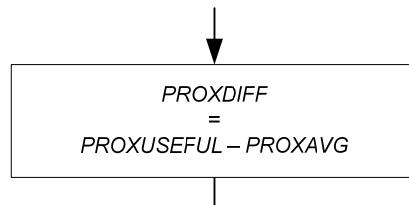

### 3.4.5. PROXDIFF Update

PROXDIFF update consists of the complementary operation i.e. subtracting PROXAVG to PROXUSEFUL to ignore slow capacitances variations ( $C_{Env}$ ) and extract only user related variations i.e.  $C_{User}$ .

**Figure 18: PROXDIFF Update**

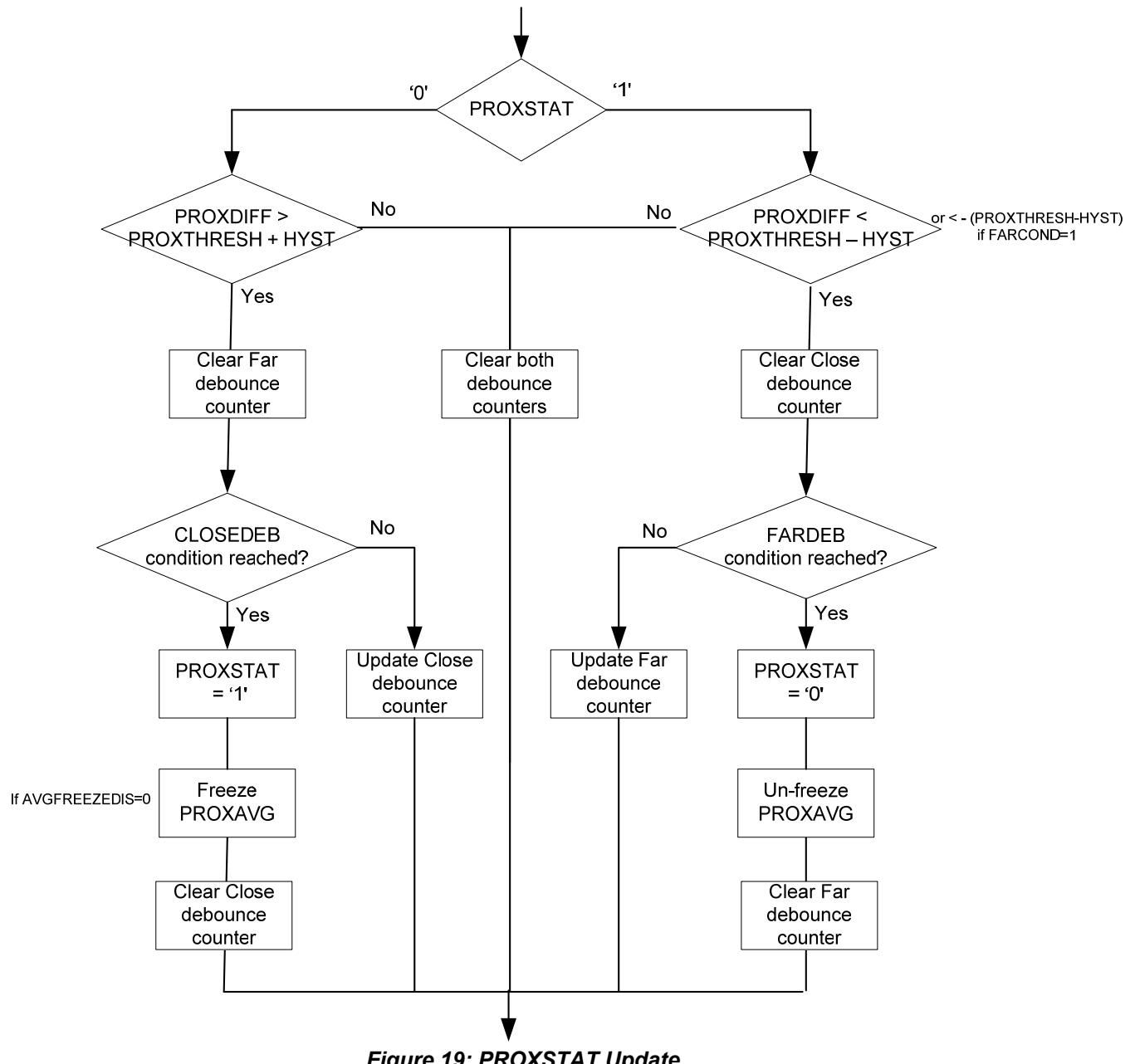

### 3.4.6. PROXSTAT Update

PROXSTAT update consists mainly of taking PROXDIFF information ( $C_{User}$ ), comparing it with a user programmable threshold PROXTHRESH and finally updating PROXSTAT accordingly. When PROXSTAT=1, PROXAVG is typically frozen to prevent the user proximity signal from being absorbed into  $C_{Env}$ .

Please refer to the application notes for further details.

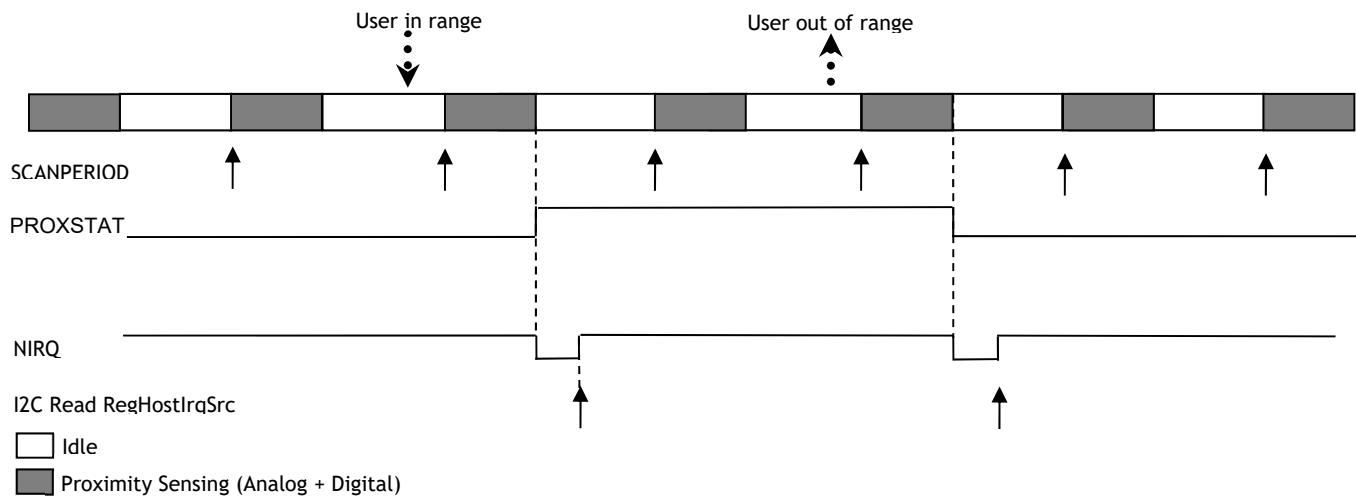

### 3.5. Host Operation

An interrupt can be triggered when the user is detected as “close” (in range), detected as “far” (out of range), or both (CLOSEANYIRQEN, FARANYIRQEN).

**Figure 20: Proximity Sensing Host Operation (Monitoring Close/Far Events)**

An interrupt can also be triggered at the end of each scan period’s conversion, indicating to the host when the proximity sensing block is running (CONVDONEIRQEN). This may be used by the host to synchronize noisy system operations or to read phase data (PROXUSEFUL, PROXAVG, and PROXDIFF) synchronously for monitoring purposes.

**Figure 21: Proximity Sensing Host Operation (Monitoring Conversion Events)**

Besides the two examples above, the interrupt can be mapped to many different status bits to accommodate application needs. Cf. register map for the details.

---

## 3.6. Operational Modes

### 3.6.1. Active

Active mode uses fixed and typically short scan periods. All phases can share the same Active scan period (SCANPERIOD) or use different ones as needed (SCANFACTOR\_PHx).

### 3.6.2. Doze

In some applications, the reaction/sensing time needs to be fast when the user is present (proximity detected), but can be slow when no detection has occurred for some time.

The Doze mode, when enabled (DOZEPEIOD), allows the chip to automatically switch between a fast scan period (SCANPERIOD) during proximity detection (by any of the enabled phase) and a slow scan period (DOZEPEIOD) when no proximity is detected. This enables lower average power consumption at the expense of longer reaction times.

After proximity is detected (by any of the enabled phases), the chip will automatically switch to Active mode. And conversely when proximity is not detected anymore (by none of the enable phases), it will automatically switch to Doze mode.

### 3.6.3. Sleep

Sleep mode can be entered by disabling all phases (PHEN=0). It places the chip in its lowest power mode, with scanning completely disabled and idle period set to continuous. In this mode, only the I2C serial bus is active (and PWM if needed). Enabling any phase (PHEN) and sending activation command will make the chip leave Sleep mode (for Doze if enabled, else Active mode).

Additionally, Sleep mode can also be entered by using the pause feature. However, unlike using PHEN, exiting Sleep mode thru unpause will not generate any compensation. If the pause request is not received during idle, the chip will first complete normally sensing+processing of the enabled phases before entering sleep.

# 4. I2C Interface

## 4.1. Introduction

The I2C implemented on the chip and used by the host to interact with it is targeted to comply with:

- Standard (100kb/s) and Fast (400kb/s) modes.

- Slave mode

- 7-bit address

- Default is 0x28 (b0101000)

- **Bit 2** will be set if CSIO2 is grounded during reset (power-up or software).

**Important:** While CSIO2 is externally grounded, it must be programmed in such a way that it's always set to GND or HZ from the chip.

The host can use the I2C to read and write data at any time, and these changes are effective immediately. Therefore the user may have to disable/enable phases(s) or perform a compensation for new settings to apply properly.

## 4.2. I2C Read/Write Format

The format of the I2C write and read are given in the figure below. Note that register address is 16-bit and register data is 32-bit.

### Write:

### Read:

From master (external host) to slave (SX9330)

From slave (SX9330) to master (external host)

S Start

Sr Repeated Start

SA 7-bit Slave Address

A Acknowledge

N Not Acknowledge

RA 16-bit Register Address

WDn 32-bit Write Data (1...n are optional)

RDn 32-bit Read Data (1...n are optional)

P Stop

**Figure 22: I2C Read/Write Format**

The register address is automatically incremented (by 4) when successive register data is supplied (WD1...WDn) or retrieved (RD1...RDn) by the master.

## 5. Reset

### 5.1. Power-Up

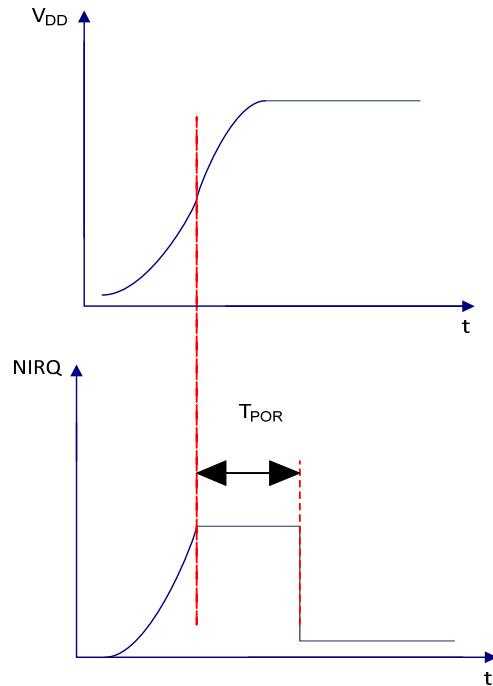

During a power-up condition, the NIRQ output is (typ.) HIGH until  $V_{DD}$  has met its minimum input voltage requirements and a  $T_{POR}$  time has expired upon which, NIRQ asserts to a LOW condition indicating that the chip is ready. If needed, the host can perform an I2C read of RegHostIrqSrc to clear this NIRQ status.

Figure 23: Power-up vs. NIRQ

### 5.2. Software Reset

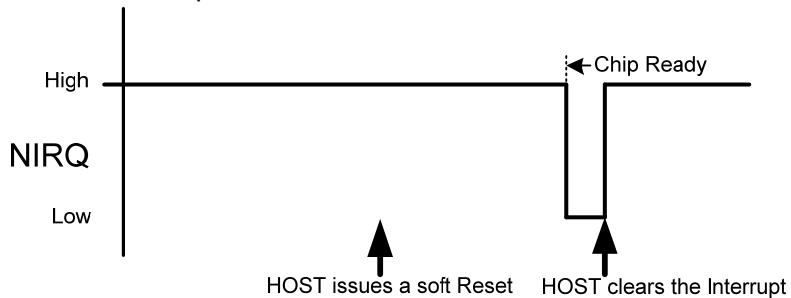

The host can also perform a reset anytime by writing 0xDE into RegReset. The NIRQ output will be asserted when the chip is ready and if needed the host can perform an I2C read to clear this NIRQ status.

Figure 24: Software Reset

---

## 6. Interrupt

### 6.1. Assertion and Clearing

Except for Reset, the interrupt pin can be asserted once per scan period at the end of the processing phase. It will be automatically cleared after the host performs a read of RegHostIrqSrc (which content will be cleared as well).

# 7. Registers

The registers below allow the user to do full parameter customization and their values must be set in accordance with the latest application notes available (please contact your Semtech representative).

Please note the following:

- a) Addresses not listed are reserved and should not be written.

- b) Reserved bits should be left to their default value unless otherwise specified.

- c) Unless stated otherwise and when applicable, default values can be considered to be typical ones.

| Addr (hex)                         | Name           | Variable        | Bits | RW | Default  | Description                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------|----------------|-----------------|------|----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Interrupt and Pause Control</b> |                |                 |      |    |          |                                                                                                                                                                                                                                                                                                                                                                        |

| 4000                               | RegHostIRQSrc  | Reserved        | 31:8 |    | h0000000 |                                                                                                                                                                                                                                                                                                                                                                        |

|                                    |                | RESETIRQ        | 7    | R  | b1       | Reset interrupt source status (i.e. reset occurred).                                                                                                                                                                                                                                                                                                                   |

|                                    |                | CLOSEANYIRQ     | 6    | R  | b0       | Close interrupt source status (i.e. any PROXSTAT rising edge).                                                                                                                                                                                                                                                                                                         |

|                                    |                | FARANYIRQ       | 5    | R  | b0       | Far interrupt source status (i.e. any PROXSTAT falling edge).                                                                                                                                                                                                                                                                                                          |

|                                    |                | COMPDONEIRQ     | 4    | R  | b0       | Compensation interrupt source status (i.e. any COMPSTAT falling edge).                                                                                                                                                                                                                                                                                                 |

|                                    |                | CONVDONEIRQ     | 3    | R  | b0       | Conversion interrupt source status (i.e. CONVSTAT falling edge).                                                                                                                                                                                                                                                                                                       |

|                                    |                | PROG2IRQ        | 2    | R  | b0       | As defined by PROG2IRQCFG.                                                                                                                                                                                                                                                                                                                                             |

|                                    |                | PROG1IRQ        | 1    | R  | b0       | As defined by PROG1IRQCFG.                                                                                                                                                                                                                                                                                                                                             |

|                                    |                | PROG0IRQ        | 0    | R  | b0       | As defined by PROG0IRQCFG.                                                                                                                                                                                                                                                                                                                                             |

| 4004                               | RegHostIRQMsk  | Reserved        | 31:7 |    | h0000000 |                                                                                                                                                                                                                                                                                                                                                                        |

|                                    |                | CLOSEANYIRQEN   | 6    | RW | b1       | Enables the close interrupt (any).                                                                                                                                                                                                                                                                                                                                     |

|                                    |                | FARANYIRQEN     | 5    | RW | b1       | Enables the far interrupt (any).                                                                                                                                                                                                                                                                                                                                       |

|                                    |                | COMPDONEIRQEN   | 4    | RW | b0       | Enables the compensation interrupt.                                                                                                                                                                                                                                                                                                                                    |

|                                    |                | CONVDONEIRQEN   | 3    | RW | b0       | Enables the conversion interrupt.                                                                                                                                                                                                                                                                                                                                      |

|                                    |                | PROG2IRQEN      | 2    | RW | b0       | Enables the PROG2 interrupt.                                                                                                                                                                                                                                                                                                                                           |

|                                    |                | PROG1IRQEN      | 1    | RW | b0       | Enables the PROG1 interrupt.                                                                                                                                                                                                                                                                                                                                           |

|                                    |                | PROG0IRQEN      | 0    | RW | b0       | Enables the PROG0 interrupt.                                                                                                                                                                                                                                                                                                                                           |

| 4008                               | RegHostIRQCtrl | Reserved        | 31:8 |    | h0000000 |                                                                                                                                                                                                                                                                                                                                                                        |

|                                    |                | Reserved        | 7    |    | b0       |                                                                                                                                                                                                                                                                                                                                                                        |

|                                    |                | HOSTIRQPINSEL   | 6    | RW | b0       | Defines which pin is used as interrupt:<br>b0: NIRQ<br>b1: CSIO4                                                                                                                                                                                                                                                                                                       |

|                                    |                | HOSTIRQPOLARITY | 5    | RW | b0       | Defines the interrupt pin polarity:<br>b0: Active Low<br>b1: Active High<br>Only applies when HOSTIRQFUNCTION=b0.                                                                                                                                                                                                                                                      |

|                                    |                | Reserved        | 4    |    | b0       |                                                                                                                                                                                                                                                                                                                                                                        |

|                                    |                | HOSTIRQFUNCTION | 3    | RW | b0       | Disables the interrupt function:<br>b0: On<br>b1: Off                                                                                                                                                                                                                                                                                                                  |

|                                    |                | PAUSEIRQEN      | 2    | RW | b0       | Enables pause function via interrupt:<br>b0: Off<br>b1: On, the chip will pause when it sets the interrupt pin active<br>Only applies when HOSTIRQFUNCTION=b0.<br>Note that before going to Sleep(pause) mode, any pending scan period measurements are completed (unlike PHEN).<br>Also, no compensation is performed when Sleep(pause) mode is exited (unlike PHEN). |

|                                    |                | PAUSESCOPE      | 1    | RW | b0       | Defines the features disabled in Sleep(pause) mode:                                                                                                                                                                                                                                                                                                                    |

|                        |              |                 |       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|--------------|-----------------|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |              |                 |       |           | b0: Sensor scanning only<br>b1: Sensor scanning and PWM Engines                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        |              | Reserved        | 0     | b0        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4010                   | RegPauseStat | Reserved        | 31:1  | h00000000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        |              | PAUSESTAT       | 0     | RW        | b0<br>When set, indicates that the chip is currently in Sleep(pause) mode.                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>Clock Spreading</b> |              |                 |       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4054                   | RegAfeCtrl   | Reserved        | 31:18 | h0000     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        |              | CLKSPREADRANGE  | 17    | RW        | b0<br>Defines the clock spreading range:<br>b0: Full (16 steps)<br>b1: Reduced (8 steps)                                                                                                                                                                                                                                                                                                                                                                                |

|                        |              | CLKSPREADEN     | 16    | RW        | b0<br>Enables the sampling frequency clock spreading:<br>b0: Off, fixed sampling frequency as defined by FREQ_PHx<br>b1: On, dynamic sampling frequency automatically varying around FREQ_PHx value at every sampling period<br>Note that this setting applies to all enabled phases and also affects PWM frequency during sensing.                                                                                                                                     |

|                        |              | Reserved        | 15:0  |           | h0400                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>PWM Engines</b>     |              |                 |       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4080                   | RegPwm       | PWMLEVELA       | 31:24 | RW        | h80<br>Defines the PWM Engine A duty cycle:<br>h00: 0%<br>Else: PWMLEVELA/255<br>Default value is ~50%.<br>Note that when enabled, the PROX2PWM engine will force this value accordingly.                                                                                                                                                                                                                                                                               |

|                        |              | PWMLEVELB       | 23:16 | RW        | h80<br>Same as PWMLEVELA for Engine B.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                        |              | Reserved        | 15    |           | b0                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        |              | PWMSTAGGERING   | 14    | RW        | b1<br>Enables PWM staggering on pins:<br>b0: Off, simultaneous edges<br>b1: On                                                                                                                                                                                                                                                                                                                                                                                          |

|                        |              | PWMENGINESELECT | 13:8  | RW        | b000000<br>Defines which PWM Engine is mapped to the different pins:<br>b0: Engine A<br>b1: Engine B<br>[13:8]=[NIRQ, CSIO4, CSIO3, CSIO2, CSIO1, CSIO0]                                                                                                                                                                                                                                                                                                                |

|                        |              | Reserved        | 7:2   |           | b000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        |              | PWMMASKENABLE   | 1     | RW        | b0<br>Disables PWM Engines during sensor scanning:<br>b0: On, PWM Engines work during sensor scanning<br>b1: Off, PWM Engines levels are fixed to PWMBLOCKEDLEVEL during sensor scanning                                                                                                                                                                                                                                                                                |

|                        |              | PWMBLOCKEDLEVEL | 0     | RW        | b0<br>Defines the PWM Engines values during sensor scanning, when PWMMASKENABLE=b1:<br>b0: 0%<br>b1: 100%                                                                                                                                                                                                                                                                                                                                                               |

|                        |              | Reserved        | 31:4  |           | h0000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        |              | PWMFREQ         | 3:0   | RW        | b1000<br>Defines the PWM refresh rate:<br>b0000: FOsc /2048 (~1953.12 Hz)<br>b0001: FOsc /4096 (~976.56 Hz)<br>b0010: FOsc /6144 (~651.04 Hz)<br>b0011: FOsc /8192 (~488.28 Hz)<br>b0100: FOsc /10240 (~390.62 Hz)<br>b0101: FOsc /12288 (~325.52 Hz)<br>b0110: FOsc /14336 (~279.01 Hz)<br>b0111: FOsc /16384 (~244.14 Hz)<br>b1000: FOsc /18432 (~217.01 Hz)<br>b1001: FOsc /20480 (~195.31 Hz)<br>b1010: FOsc /22528 (~177.55 Hz)<br>b1011: FOsc /24576 (~162.76 Hz) |

|                           |             |                 |       |    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------|-------------|-----------------|-------|----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |             |                 |       |    |          | b1100: FOsc /26624 (~150.24 Hz)<br>b1101: FOsc /28672 (~139.50 Hz)<br>b1110: FOsc /30720 (~130.20 Hz)<br>b1111: FOsc /32768 (~122.07 Hz)<br>Cf. FOsc/FTrim/FTemp/FVDD in electrical specifications.                                                                                                                                                                                                                                                                    |

| <b>Miscellaneous</b>      |             |                 |       |    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 41C4                      | RegI2cAddr  | Reserved        | 31:7  |    | h0000000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                           |             | I2CADDR         | 6:0   | R  | b0101000 | Indicates the current I2C address.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4240                      | RegReset    | Reserved        | 31:8  |    | h000000  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                           |             | SOFTRESET       | 7:0   | W  | h00      | Writing hDE resets the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4280                      | RegCmd      | Reserved        | 31:4  |    | h0000000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                           |             | COMMAND         | 3:0   | RW | b0000    | Writing the following values triggers the corresponding command:<br>b1111: Enables the phases specified by PHEN<br>b1110: Compensates the phases specified by COMPEN<br>b1101: Enters Sleep(pause) mode<br>b1100: Exits Sleep(pause) mode<br>After Command is sent, wait for 1 Scan Period minimum (i.e. Sensing time configured) to allow device change to occur.<br>During command execution, COMMANDBUSY=b1 and no new command should be sent until COMMANDBUSY=b0. |

| 4284                      | RegTopStat0 | Reserved        | 31:1  |    | h0000000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                           |             | COMMANDBUSY     | 0     | RW | b0       | When set, indicates that a command is currently being executed.                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>Pins Configuration</b> |             |                 |       |    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 42C0                      | RegPinCfg   | Reserved        | 31:26 |    | b000010  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                           |             | PINCFGINEN      | 25:20 | RW | b000000  | Enables the input function of the pin:<br>b0: Off<br>b1: On<br>[25:20]=[NIRQ, CSIO4, CSIO3, CSIO2, CSIO1, CSIO0]<br>Note that RegPinCfg defines the behavior of the pins outside of sensing, while during sensing it is defined by RegAfePhPhx.                                                                                                                                                                                                                        |

|                           |             | PINCFGOUTEN     | 19:14 | RW | b000000  | Enables the output function of the pin:<br>b0: Off<br>b1: On<br>[19:14]=[NIRQ, CSIO4, CSIO3, CSIO2, CSIO1, CSIO0]<br>Note that RegPinCfg defines the behavior of the pins outside of sensing, while during sensing it is defined by RegAfePhPhx.                                                                                                                                                                                                                       |

|                           |             | CSIOCFGSLEWRATE | 13:12 | RW | b00      | Defines the slew rate control for the pins NIRQ and CSIOx:<br>b00: Fastest<br>b01: Fast<br>b10: Slow<br>b11: Slowest<br>This setting applies to both edges for CSIOx and only to the falling edge for NIRQ.                                                                                                                                                                                                                                                            |